## Workfunction Tuning Technique for Dual-Gate CMOS with Single Metal Gate

Kentaro Shibahara

Research Center for Nanodevices and Systems, Hiroshima University 1-4-2, Kagamiyama, Higashihiroshima, 739-8527 Japan

Phone +81-824-24-6267, FAX: +81-824-22-7185, s-mail: shiba@sxsys.hiroshima-u.ac.jp

## 1. Introduction

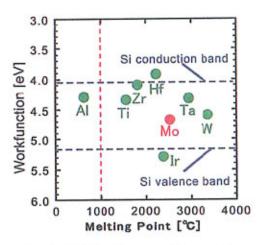

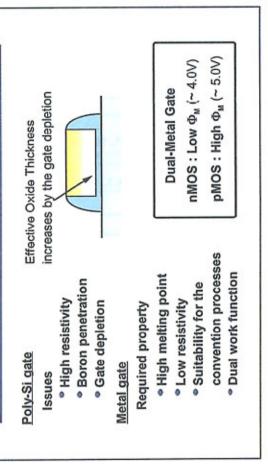

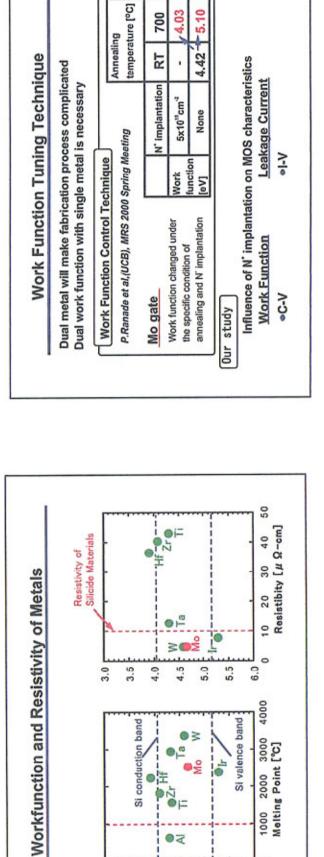

Gate oxides for leading edge production MOS devices, which are the most important factor for improving the performance of FETs, are becoming thinner than 1.5 nm. As the gate oxide is scaled, the increase in electrical thickness due to gate depletion becomes more severe. The total loss in electrical thickness due to gate depletion and quantum effects in a channel is estimated to be about 0.7 nm. This value is too large compared with physical equivalent oxide thickness. A metal gate will relieve this loss about by half. Refractory metals, such as Mo, Ta, Ti, and W, and their nitrides are candidates for metal gate materials. Their workfunction and melting point are shown in Fig. 1. Their robustness against high-temperature processes like S/D activation annealing is necessary feature as a gate electrode material. However, for CMOS devices application workfunction of metal gate must be adjusted to that for p\*-poly-Si or n\*-poly-Si.

In this report, evaluation of Mo workfunction tuning technique and brief prospect are described.

## 2. Mo workfunction tuning with Nitrogen

Wakabayashi et al. [1] reported workfunction tuning of TiN by N<sup>+</sup> implantation. This method was based on composition tuning by high dose N<sup>+</sup> implantation. Because of narrow tuning width, this method is not practical. Ranade et al. [2] reported Mo workfunction tuning also by N<sup>+</sup> implantation with negligible composition change. We have evaluated influences of N<sup>+</sup> implantation on interfaces and gate oxides [3].

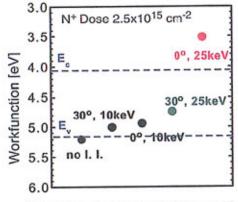

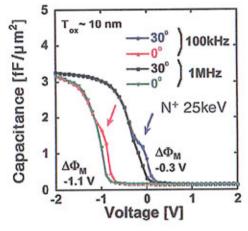

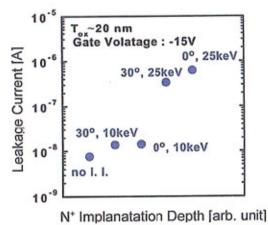

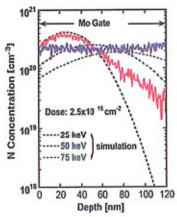

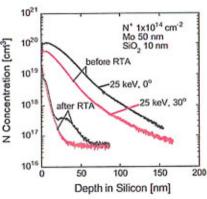

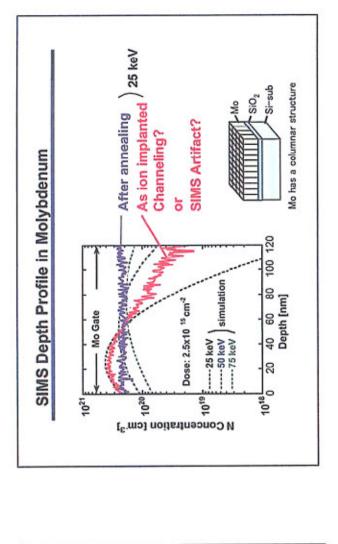

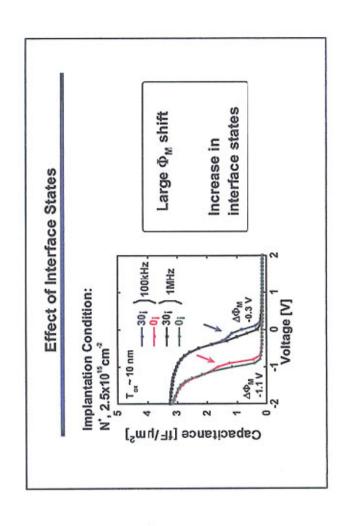

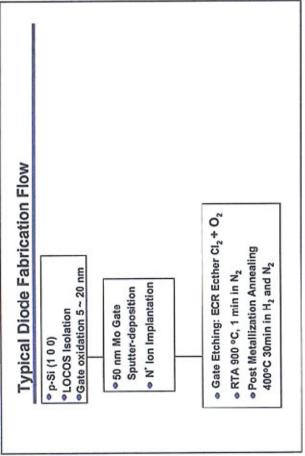

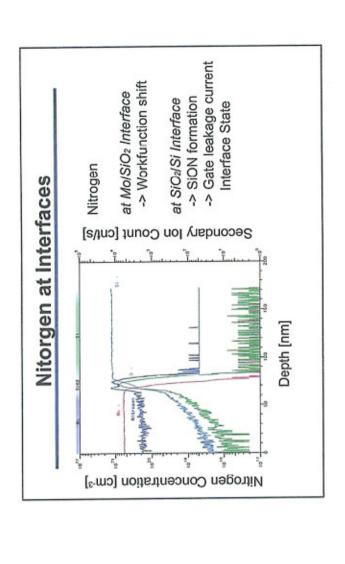

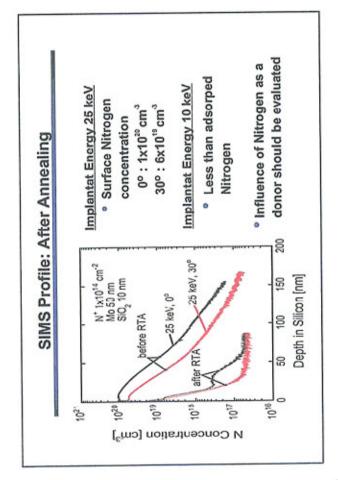

Figure 2 shows fabrication process flow of Mo gate MOS diodes. MOS diodes with various oxide thickness were fabricated for one N+ implantation condition to extract workfucntion and fixed charge density from C-V characteristics. The workfunction obtained by this method is noted as apparent workfunction in this report. RTA at 900°C for I min was carried out after N+ implantation. The apparent workfunction did not depend on RTA condition. Figure 3 shows the extracted apparent workfunction. N+ implantation dose was 2.5x1015 cm-2. Implantation depth was varied by implantation energy and angle. In the case of no N+ implantation Mo showed the apparent workfunction equivalent to p\*-poly-Si. As the implantation depth becomes deeper the apparent workfunction shifted lower. However, interface and oxide damage were observed in deep N+ implanted specimens, as shown in Figs. 4 and 5. C-V characteristics for such MOS diodes in Fig. 4 shows humps that imply interface state generation. Gate leakage current increased as the N+ implantation became deeper. Figures 5 and 6 show nitrogen profiles in Mo and Si, respectively. 25 keV N+ implantation that was effective for apparent workfunction tuning leads to N+ implantation into Si substrates through gate

oxides. The implanted nitrogen in Mo diffuses very fast during RTA and forms nearly uniform profile as shown in Fig. 6. The most part of nitrogen in Si disappears after RTA, as shown in Fig. 7, that implies oxinitride formation at the SiO<sub>2</sub>/Si interface. We have tried optimizing shallow implantation condition to obtain workfucntion shift without these influences by nitrogen, however, it was not successful to date.

## 3. Direction to future research

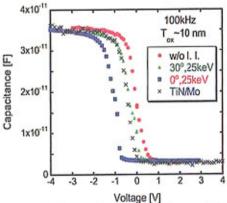

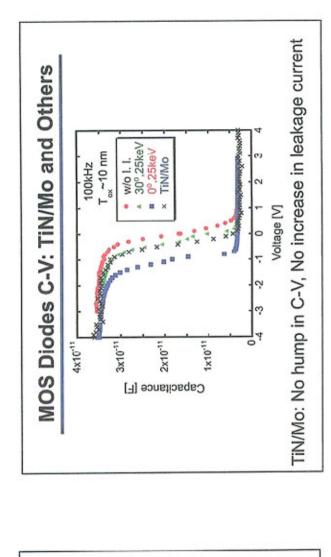

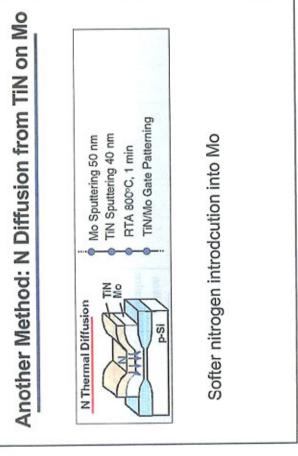

From an application view point, effectiveness of the N+ implantation should be evaluated by MOSFET Vth shift and channel mobility. Ranade et al. [4] reported MOSFET with N+ implanted Mo showed reasonable Vth shift, however they recently commented that mobility degradation is caused by the N+ implantation. Figure 8 shows C-V characteristics of TiN capped Mo MOS diodes. Apparent workfunction shift was also obtained by nitrogen thermal diffusion from TiN. The TiN/Mo MOS diodes showed no degradation found in the N+ implantation cases. However, recently we found that the apparent workfunction shift in a TiN/Mo structure was reversible by additional thermal process after removing TiN. These results indicate that nitrogen transported by thermal diffusion is not stable at the Mo/SiO2 interface and easily diffuse out. On the contrary, nitrogen introduced by the N+ implantation was stable at the interface because additional thermal treatment did not affect. However, the N+ implantation involved the counter effects. In general, if we can fabricate a stable atomic layer at the metal/insulator interface, workfunction shift due to electric dipole formation is expected. Impurity pileup caused by thermal treatment has possibility to match this claim. Snowplow effect due to silicidation is a considerable candidate [5].

## 4. Summary

We have evaluated Mo workfucntion tuning by N<sup>+</sup> implantation and nitrogen thermal diffusion. The former showed large apparent workfucntion shift, however, damage due to the implantation was not negligible. The later also showed the apparent workfucntion shift but it was not thermally stable. These methods should be improved or other methods should be found to apply workfucntion tuning technique to practical devices.

## References

- 1. H. Wakabayashi et al. 1999 IEDM Tech. Digest p. 253.

- P. Ranade et al , MRS. Proc., 611 (2000) p. C3.2.1.

- T. Amada et al., MRS Proc., 716 (2002) p. 299.

- 4. Q. Lu et al , Digest 2001 VLSI Tech. Symp. p. 45.

- W.P. Masazara et al, 2002 IEDM Tech. Digest p. 367.

Fig. 1 Workfunction and melting point

N\* Implanatation Depth [arb. unit]

of metal materilas.

Fig. 2 Fabrication process flow of MOS diodes for workfunction evaluation.

Fig. 3 Workfunktion extracted from Mo gate MOS diodes with N+ implantation.

Fig. 4 Influence of N+ implantation on Mo gate MOS diode C-V characteristics.

Fig. 5 Leakage current enchanced by N+ implantation in Mo gate MOS.

Fig. 6 Nitrogen depth profiles in Mo obtained by SIMS (solid lines) and simulation (dashed lines).

Fig. 7 Nitrogen SIMS depth profiles in Si substrates for before and after RTA. RTA temperature and time were 900°C and 1 min, respectively.

Fig. 8 Comparison of C-V characteristics for a TiN/Mo gate diode with that for N+ implanted diodes.

# Workfunction Tuning Technique for Dual-Gate

Necessity of the Metal Gate and Required Property

CMOS with Single Metal Gate

Kentaro Shibahara

Research Center for Nanodevices and Systems

Hiroshima University

Si conduction band

3.5

0,0

4.5

5.0

4.0

Si valence band

5.5

1000 2000 3000 Melting Point [°C]

4.03

700

30°, 25keV

no I. I.

Voltage [V]

5.0 E

- no l. l.

3.5

Frequency: 1MHz

Tox~ 10 nm

C-V Characteristic andWork Function

Implantation Condition: N, 25 keV, 2.5x10<sup>15</sup> cm<sup>-2</sup>

## Issues of Diffusion from TiN/Mo

Diffusion time, temperature and N composition in TiN

-> Not Effective for Φ<sup>m</sup> Control

Thermally Reversible

## Other Methods?

Keywords: Pileup of Impurities

Where?: Metal/Insulator Interface

ex. Snowplow effect during silicidation

What elements?

Any elements stable at the interface

-> electric dipole formation and Φm shift

## Summary

- Work function control by N

implantation in Mo gate MOS structure

- <sup>®</sup> Φ<sub>M</sub> shift from 5.2 eV to 4.0 eV Surface Nitrogen concentration ~ 1x10<sup>20</sup> cm<sup>3</sup>

- Problems: Leakage current and interface states

→ More detailed evaluation of the Mo/ SiO<sub>2</sub> / Si interfaces is necessary

- Solid Phase Diffusion from TiN: less Damage How to change workfunction shift?

## Acknowledgements

The data shown here are obtained by cooperative work at RCNS with Mr. T. Amada, Mr. M. Hino and Dr. N. Maeda.

Part of this work is supported by STARC (Semiconductor Technology Academic Research Center).