## 三次元 MOS トランジスタの研究開発

研究代表者: 角南英夫(ナノデバイス・システム研究センター教授、先端研半導体集積科学専攻)研究分担者: 奥山清 (COE 研究員)、片上朗 (先端研量子物質科学専攻平成 15 年度修了)、

子林景(先端研量子物質科学専攻 M1)、松村俊平(工学部第二類 B4)

## 1. 研究目的

1970 年代に始まったシリコン集積回路の大規模化・高密度化はこの 30 年間にほぼ 100 万倍の性能・規模向上が達成された。最大の原動力はトランジスタの微細化であり、当初  $10\mu m$  であったトランジスタのゲート長は 15 年で 1/10、30 年で 1/100 になった。現在は  $100nm(0.1\mu m)$  のゲート長のトランジスタが量産されようとしている。いっぽう、研究段階ではその寸法に見合った性能は得られていないが、すでにゲート長 5nm のトランジスタが試作されている 10。

しかし、トランジスタが微細になるに伴い、主に短チャネル効果と呼ばれる特性障害が発生している。ドレインに印加する電圧によって電流を制御する機能、たとえばしきい電圧の変化、遮断電流の増加など、特性が悪化するものである。

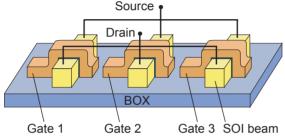

この短チャネル効果抑制のため、チャネルやソース・ドレイン (S/D) 近傍の不純物分布の精密制御、ゲート絶縁膜の薄膜化などが工夫されてきたが、限界が訪れている。この解決のため、従来の平面から三次元的にトランジスタを構成する試みがなされている。それらは、酸化によって基板と絶縁した Si ビームを用いる DELTA<sup>2)</sup>、SOI 層の上下に設けたダブルゲート構造 <sup>3)</sup>、ごく薄いビームをチャネルとする FIN-FET<sup>4)</sup> 構造などである。

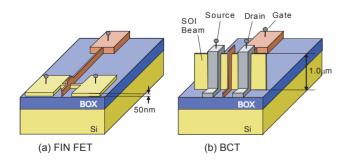

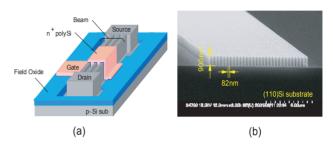

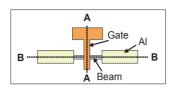

Fig. 1 FINFET (a) as a representative of 3-D transistor and a beam channel transistor, BCT under study.

三次元トランジスタの研究開発ではすでにトランジスタの動作限界に近いゲート長 10nm まで発表されている。図1に示すように、この三次元トランジスタは縦方向に伸びたビームの側壁をチャネルとすることから、ビームを高くすれば単位平面あたりの駆動電流を増大することができる。

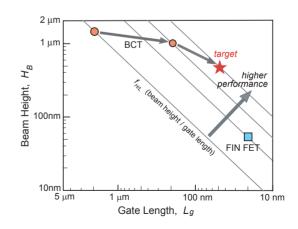

本研究はこれを達成するため、図1(b)に示すような高いビームのトランジスタの実現を目指した。表1に研究目的と主な課題を示す。また、このような三次元構造形成の難易度は高さの絶対値よりはむしろ平面寸法との比、すなわちアスペクト比であり、アスペクト比で評価した本研究の位置づけを図2に示す。

#### 表 1 本研究の目的と技術課題

- A. 500nm 以上の高い Si ビームに形成した三次元 MOS トランジスタ

- ・課題 (a-1) 高い Si ビームの形成技術 (a-2) 高い Si ビームへのゲート形成 (a-3) 高い Si ビームへの不純物ドーピング (a-4) 高い Si ビームへの S/D 電極接続

- B. 500nm 以下の低い Si ビームに形成した高度な 自己整合 MOS トランジスタ構造

- ・課題 (b-1) 高度な自己整合プロセス

Fig. 2 A figure of merit of beam height / gate length,  $f_{\rm H/L}$  of 3-D transistor.

## 2. 研究開発結果

## 2.1 高い Si ビームの形成技術

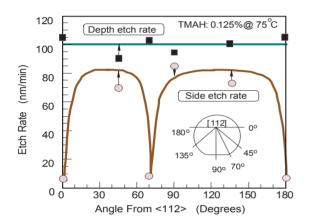

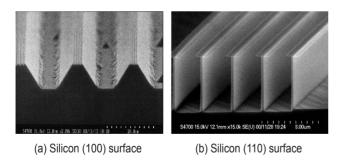

現在の方向性ドライエッチング RIE(reactive ion etching) 技術を用いれば、高いアスペクト比の Si ビームを得ることは可能であるが、さらに高い急峻なビームを形成するには、たとえば TMAH(tetra methyl ammonium hydroxide) を用いることができる。これは TMAH では図3に示すように、Si の (111) 面のエッチング速度が極端に遅いことを利用するもので、(110)Si 面にきわめて垂直性の高い急峻なビームを形成できる。図4にはその結果の一部を示した $^{5}$ 。表2は代表的な材料のエッチング速度の値を示す。

Fig. 3 Etch rate of TMAH on (110) Si surface. Extremely low etch rates correspond to those for (111) surface.

Fig. 4 Obtained cross sections of Si (100) (a) and Si (110) with TMAH etchant.

Table 2 Etch rates of TMAH (2.5% aqueous solution at  $75^{\circ}$ C).

| Material         | Etch Rate  | Ratio |

|------------------|------------|-------|

| (110) Si         | 606 nm/min | 30    |

| (111) Si         | 30 nm/min  | 1     |

| SiO <sub>2</sub> | 0.8 nm/min | 0.04  |

この Si ビームを図 3(b) に示すように複数本並べてそれらにまたがるようにゲートを形成した図 5に示すようなトランジスタを実現した $^6$ 。ビームの高さは 900nm、厚さは 82nm である。このトランジスタの  $I_{d}$   $V_{d}$  特性を図 6 に示す。基板は 80  $\Omega$ -cm でチャネルドーピングを行っていないのでしきい電圧は負となっているが、キャリヤ移動度、ゲート耐圧の低下などトランジスタ特性に異常は見られずは正常である。

Fig. 5 A bird's eye view (a) and an SEM image of etched SI beams. surface.

Fig. 6  $I_d$ - $V_d$  and  $I_d$ - $V_g$  characteristics of corrugated channel transistor, CCT. Obtained threshold voltages below 0 V are due to high reistivity substrate (80  $\Omega$ -cm) and no channel doping.

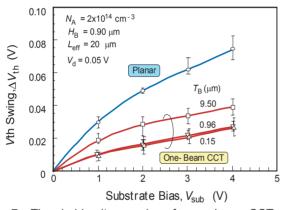

図7にしきい電圧の基板バイアス依存性を示す。ビーム厚さ  $T_B$  が  $0.96\mu m$  以下でしきい電圧変化が重なっているのは、ビーム内が完全に空乏化されていることに他ならない。

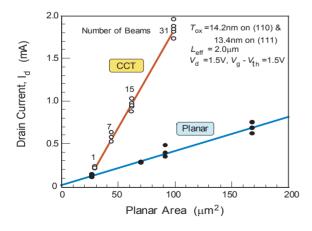

このCCTの平面に勝る特長を単位面積当たりのドレイン電流という指標で評価すると図8のような特性となる。ビーム本数が増すと本数に比例して駆動ドレイン電流が増加する特性を示している。したがって、ビームを高くできればそれに応じて駆動電流をますことができる。

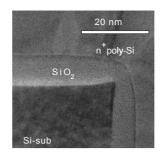

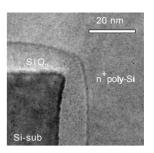

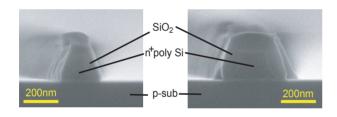

このようなビームに形成したトランジスタの一つの課題に、ゲート耐圧の低下が想定される。図9はビームの上部、下部でゲートSiO<sub>2</sub>膜が薄くなっている様子を示す。ただ、トランジスタの微細化に伴って印加電圧も3V以下に低下しているので実質上の問題はないと考えられる。

Fig. 7 Threshold voltage swings for one-beam CCT and planar transistor. Note that curves with beam thickness  $T_{\rm B}$  of below 0.96  $\mu \rm m$  are equivalent.

Fig. 8 Drain currents of CCT's with number of beams of from 1 to 31. Almost 5-fold increase is obtained compared to planar transistor at a planar are of 100  $\mu$ m<sup>2</sup>.

(a) 850 °C

(b) 1000 °C

Fig. 9 Cross-sectional TEM images for oxide thinning at beam edges.

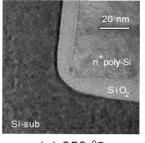

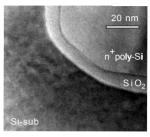

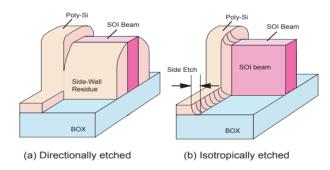

#### 2.2 高い Si ビームのゲート形成

通常の強い方向性をもつドライエッチングを用いると、図 6(a) に示すようにビームの側面にゲート材料たる多結晶 Si が残存する。高いビームにゲートをまきつけるには、現在のところ図 6(b) に示すような等方性エッチングしかないといえよう。この場合には、微細加工性が問題となる。

Fig. 10 Gate electrodes formed by anisotropic etching (a) or isotropic etching (b). Cross-sectional TEM images for

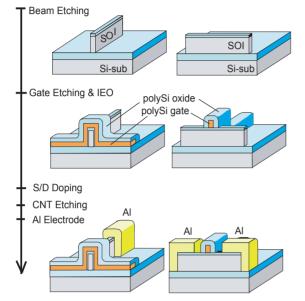

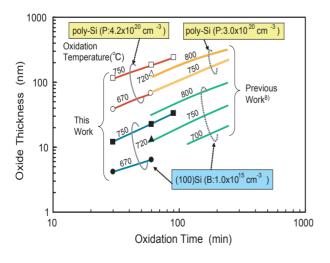

この問題を軽減するプロセスを考案した<sup>7)</sup>。図 11 に示すように、十分リンや砒素を添加した多結晶 Si ゲートを等方性エッチングで加工した後、低温の湿式酸化を行う。酸化温度が 800℃以下では、多結晶 Si を基板上の酸化膜厚の 10 倍以上の厚さの自分自身の酸化膜で覆うことが可能である<sup>8)</sup>。その一例を図 12 に示す。また不純物濃度依存酸化の結果を図 13 に示す。

(A-A cross section) (B-B cross section)

Fig. 11 A proposed process sequence of beam channel transistor.

Fig. 12 Polysilicon gates wraped by their own oxide.

Fig. 13 Experimental results of impurity enhanced oxidation, IEO.

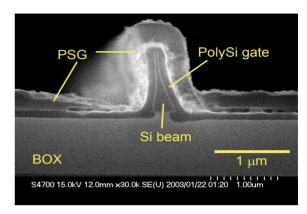

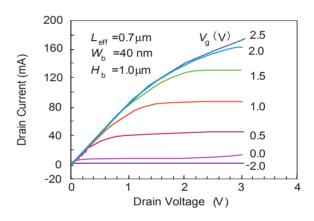

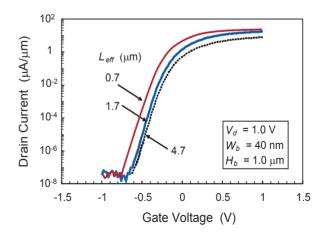

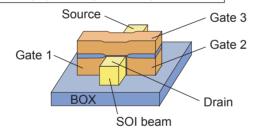

これによって試作した SOI(silicon-on-insulator) 基板上のビームチャネルトランジスタの断面図を 図 14 に、図 15 に  $I_{d}$ - $V_{d}$  特性を、図 16 に  $I_{d}$ - $V_{g}$  特性を示す。正常な動作を示している。

Fig. 14 A cross section of SOI beam channel transitor with 1.0- $\mu$ m high SOI beam. $\Omega$ -cm) and no channel doping.

Fig. 15  $I_d$ - $V_d$  characteristics for beam channel transistor with 1.0- $\mu$ m high and 40-nm thick SOI beam and 0.7- $\mu$ m channel length. No channel implantation causes weak cut-off.

Fig. 15  $I_d$ - $V_g$  characteristics for beam channel transistor with 1.0- $\mu$ m high and 40-nm thick SOI beam and 0.7- $\mu$ m channel length. No channel implantation causes weak cut-off.

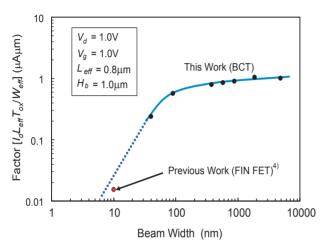

MOSトランジスタの性能指標の一つは、指標  $[I_dL_{ef}T_{ox}/W_{ef}]$  である。この値は直接電界効果移動度に結びつくものであり、トランジスタが問題なく作成されているか否かの指標になる。図 17 にビームチャネルと、FINFET のデータを示す。ビーム幅が 100nm 以下で急激に指標が下がっているがこれはビームチャネルの本質的な問題であろう。少なくともビーム幅には実質的な下限値があると考えるべきであろう。

Fig. 17 Dependence of a factor,  $[I_c L_{eff} T_{ox}/W_{eff}]$  on beam width. cut-off.

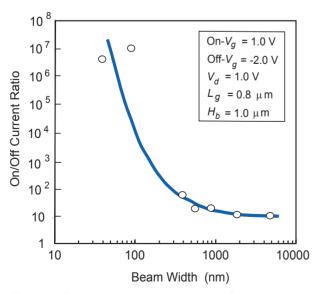

また、短チャネルトランジスタではオフ電流の上昇が大きな問題となるが、相対的にはオン電流との比が問題になる。ここまでのデータをまとめて、オン電流/オフ電流特性を図18に示す。

Fig. 18 Beam width dependence of on-current to off-current ratio for SOI BCT ( $T_{\rm OX}$ =10 nm).

#### 2.3 高い Si ビームへの不純物ドーピング

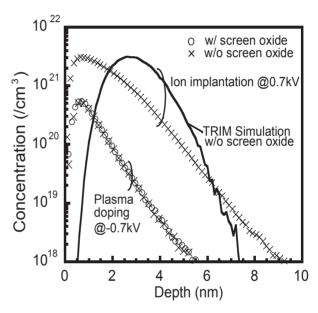

図 4(b) に示したような、高くてピッチの詰まった Si ビームの側壁に均一にドーピングするには、通常用いられているイオン注入法には限界がある。斜めに打ち込んでも、深い溝の下部には到達しがたい。そこで、等方性の強いプラズマドーピングの適用を図っている。

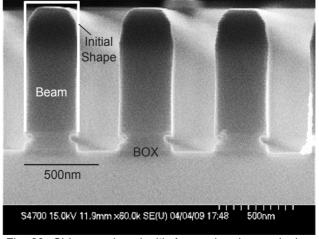

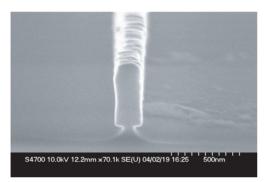

同じ中心加速電圧での不純物分布をイオン注入 と比較して図 19に示す。そのときのビーム形状 を図 20に示す。プラズマのエネルギーによって ビーム上部のとくに角の部分が削れていることが わかる。実用上支障がないよう調整が必要である。

Fig. 19 Srsenc SIM profiled for ion implantation and plasma doping.

Fig. 20 Si beams doped with Arsenc by plasma doping. Top edges are sputtered and scraped off by Ar plasma at -700-V bias.

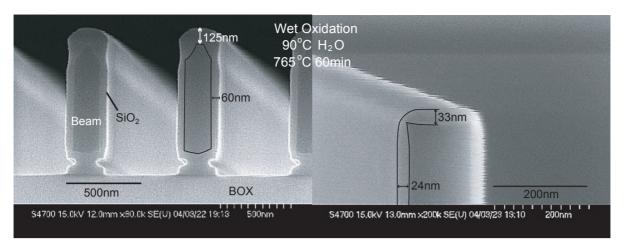

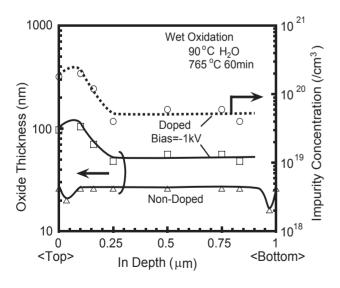

Fig. 21 Cross-sectional SEM images of As-plasma doped Si beam (a) and non-doped Si beam (b) after wet oxidation at 765°C for 60 min. Oxide thickness closely relates impurity concentration.

現在、垂直な Si ビームの側壁へのドーピング 分布を直接測定する方法がない。そこで、低温湿 式酸化では、酸化速度が強く不純物濃度に依存す ることを利用して、ビーム表面の不純物濃度分布 を評価した。酸化後のビーム断面を図 21 に、お よびこれから評価した不純物濃度分布を図 22 に 示す。上面多量にドーピングされているが側面は ほぼ均一にドーピングされていることがわかる。 ドーピングをしないビームの上端部、下端部の落 ち込みは図 21(b) でわかるようにエッジ部の酸化 膜の薄層化である。これは、低温酸化では酸化膜 の粘性が低く、かつ機械応力によるといわれる。

Fig. 22 Measured oxide thickness profile and doped impurity profile for 1.0- $\mu$ m high Si beam, indirectly evaluated from the oxide profile.

## 2.4 高い Si ビームの S/D 電極接続

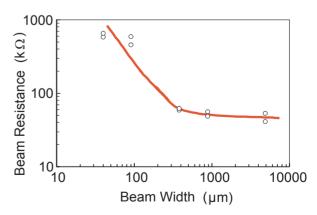

図1に示したような高いビームのソース/ドレイン (S/D) への金属電極を最上面だけで接続すると、ビーム下部のチャネルには長い距離の S/D 部を通じて電流が流れる。これはソースに生じる寄生抵抗が増大したことに相当し、トランジスタ特性を劣化させる。 図 23 にここで得られたビーム抵抗の幅依存性を示す。幅が 300nm を超えると一定となるのは、リンの拡散層の厚さが一定となるためである。

ビームチャネルトランジスタではとくに 100nm より薄いシリコンビームを用いるので、ソース・ドレインの抵抗は無視できない。したがって、S/D 部は十分抵抗が低いか、あるいは金属電極が S/D 側面部の全面を覆う必要がある。ソース・ドレインの抵抗を実質的に低減する方法は次のようなものがある。

Fig. 23 Beam width dependence of beam resistance for phosphorus-doped Si beam.

- (1) ソース・ドレイン拡散層をシリサイド化 する。

- (2) ソース・ドレインにシリコンやゲルマニ ウムを被着して厚くする。

- (3) ソース・ドレイン拡散層を金属で覆う。

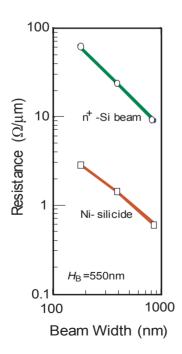

本研究ではシリサイド化の予備実験を行っている。図 24 のようなリンを添加した Si ビームにスパッタにより 100nm 厚の Ni を被着して 500℃、30 分の真空アニールを行う。これにより図 25 に示すようなビーム抵抗のビーム幅依存性が得られた。またこれらから抵抗率を評価すると次のようになった。

- ・ $n^+$ -Si ビーム 抵抗率 =  $4.2x10^4 \Omega$ -cm

- ・Ni シリサイド層 抵抗率 =  $2.5 \times 10^{-5} \Omega$  -cm

Beam height/width=550 nm/180 nm Fig. 24 Ni-silicided Si beam.

Fig. 25 Resistance of Ni-silicided S/D

この値からほぼ良好なシリサイドが得られていることがわかった。この実験では孤立ビームのみの値を評価したが、Niの被着状態が重要な要素となるので、今後密に形成されている場合の制約を調べる必要がある。

#### 3 結論と今後の計画

本研究では、ビームの高さが 1.5μm でゲート長が 2.0μm、さらにはビーム高: 1.0μm でゲート長: 0.2μm のトランジスタを実現した。ビームの高い三次元トランジスタは、本質的にチャネル幅を小さくできないから LSI の大部分を構成するトランジスタには適用できない。応用は、小さな平面面積で大きな電流を得る用途であり、その意味でパワートランジスタがふさわしい。特に、下記のような応用が考えられる。

- (1) 単体のパワートランジスタ

- (2) パワートランジスタを内蔵した無線 送受信チップ

- (3) 超低電力 LSI の電力制御トランジスタ。

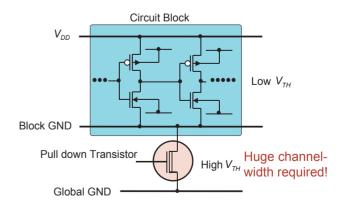

などである。(3) は図 26 に示すように、LSI の機能ブロックに直列に制御トランジスタを挿入し、これを流れる電流を制御することでブロック全体の消費電力を、時分割で制御する<sup>9)</sup>。動作させないときや、低速で動作させるときには電流を制限すればよい。高速に動作するときには制御トランジスタ自身の抵抗は極力小さい必要があるから、電流駆動能力が大きければ大きいほど有利である。本研究で開発した、櫛型やビームチャネルには格好の応用先と考えられる。

Fig. 26 An idea to control power/operation speed with each circuit block 9).

極微細トランジスタに関しては、他研究機関か ら高さ 50nm ゲート長 10nm のトランジスタがす でに発表されている。アスペクト比を考慮すると、 本研究では高さ 200nm でゲート長 20nm を実現 したいが、微細化だけではすでに大きな成果とい えない状況にある。

そのため、三次元構造を高度に利用した自己整 合トランジスタの実現を計画している。その一つ の提案を図27に示す。ビームの三面をそれぞれ 別個のトランジスタとして構成し、根本的な高密 度化を達成することが出来る。

# Conventional parallel connection of 3 transistors

Proposed parallel 3-transistor connection with highly self-alighed configuration

Fig. 27 Three transistors connected in pallarel with highly self-aligned configuration.

#### 参考文献

- 1) H. Wakabayashi, S. Yamagami, N. Ikezawa, A. Ogura, M. Norihiro, K. Artai, Y. Ochiai, K. Takeuchi, T. Yamamoto, and T. Mogami, IEDM Tech. Dig., pp. 989-992, 2003.

2) D. Hisamoto, T. Kaga, and E. Takeda, IEEE Trans. Electron

- Devices, 38, pp. 1419-1425,1991

- 3) H-S. P. Wong, D. Frank, and P. Solomon, IEDM Tech. Dig, pp. 407-410, 1998.

- 4) Ŷ-K. Choi, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Anderson, T-J King, J. Bokor, and C. Hu, IEDM Tech. Dig. pp. 421-424,

- 5) H. Sunami, T. Furukawa, and T. Masuda, Sensors and Actuators A111, pp. 310-316, 2004.

- 6) T. Furukawa, H. Yamashita, and H. Sunami, Jpn. J. Appl. Phys., Vol. 42, pp. 2067-2072, 2003.

- 7) A. Katakami, K. Kobayashi, and H. Sunami, Jpn. J. Appl. Phys., Vol. 43, pp. 2145-2150, 2004.

- 8) H. Sunami, J. Electrochem. Soc., Vol. 125, pp. 892-897,

- 9) T. Inukai, M. Takamiya, K. Nose, H. Kawaguchi, T. Hiramoto, T. Sakurai, CICC Tech. Dig., pp. 409-412, May 2000.

## <これまでの研究成果>

## (ジャーナル論文)

- 1)T. Furukawa, H. Yamashita, and H. Sunami, "A Proposal of Corrugated-Channel Transistor (CCT) with Vertically-Formed Channels for Area-Conscious Applications," Jpn. J. Appl. Phys., Vol. 42, Part 1, No. 4B, pp. 2067-2072, April 2003.

- 2) A. Takase, T. Kidera, and H. Sunami, "Field-Shield Trench Isolation with Self-Aligned Field Oxide," Jpn. J. Appl. Phys., Vol. 42, Part 1, No. 4B, pp. 2100-2105, April 2003.

- 3) H. Sunami, T. Furukawa, and T. Masuda, "A Three-Dimensional MOS Transistor Formation Technique with Crystallographic Orientation-Dependent TMAH Etchant," SENSORS and ACTUATORS A: PHYSICAL, A111, pp. 310-316, 2004.

- 4) A. Katakami, K. Kobayashi, and H. Sunami, "A High-Aspect Ratio Silicon Gate Formation Technique for Beam-Channel MOS Transistor with Impurity-Enhanced Oxidation," Jpn. J. Appl. Phys., Vol. 43, No. 4B, pp. 2145-2150, April 2004.

#### (国際会議)

- 5) H. Sunami, T. Furukawa, and T. Masuda, "Orientation-Dependent Anisotropic TMAH Etchant Applied to 3-D Silicon Nanostructure Formation," Proc. Pacific Rim Workshop on Transducers and Micro/nano Technologies, pp. 367-372, Xiamen, July 22-24, 2002.

- 6) T. Furukawa, H. Yamashita, and H. Sunami, "Corrugated-Channel Transistor (CCT) for Area-Conscious Applications," Extended Abstracts of International Symp. on Solid State Devices and Materials, Abs. No. A-3-2, pp. 139-140, Nagoya, Sept. 17-19, 2002.

- 7) A. Takase, T. Kidera, and H. Sunami, "Field-Shield Trench Isolation with Self-Aligned Field Oxide," Extended Abstracts of International Symp. on Solid State Devices and Materials, Abs. No. A-7-4, pp. 694-695, Nagoya, Sept. 17-19, 2002

- 8) A. Katakami, K. Kobayashi, and H. Sunami, "High-Aspect Ratio gate Formation of Beam-Channel MOS Transistor with Impurity-Enhanced oxidation of Silicon Gate," Extended Abstracts of International Symp. on Solid State Devices and Materials, Abs. No. D-5-2, pp. 282-283, Tokyo, Sept. 16-18, 2003.

- 9) K. Kobayashi, T. Eto, K. Okuyama, K. Shibahara, and H. Sunami, "An Impurity-Enhanced Oxidation Assisted Doping Profile Evaluation for Three-Dimensional and Vertical-Channel Transistors," submitted to International Symp. on Solid State Devices and Materials 2004.