A Single Chip UWB Transmitter Based on 0.18µm CMOS Technology for Wireless Interconnection Pran Kanai Saha, Nobuo Sasaki and Takamaro Kikkawa Research Centre for Nanodevices and Systems, Hiroshima University

Research Center for Nanodevices & Systems, HIROSHIMA UNIVERSITY

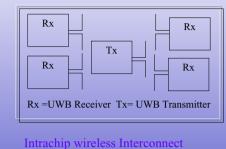

⇒ Require advanced wireless interconnect system to overcome interconnect delay problem in future ULSI

Interchip wireless Interconnect

Shannon's Theory

$C = B \log_2 \left( 1 + \frac{S}{N} \right)$

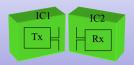

High capacity wireless interconnect system requires wide bandwidth Transmitter, Receiver and Antenna.

Research Center for Nanodevices & Systems, HIROSHIMA UNIVERSITY 🥻

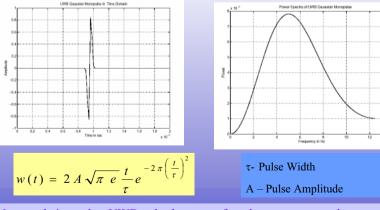

**UWB PULSE**

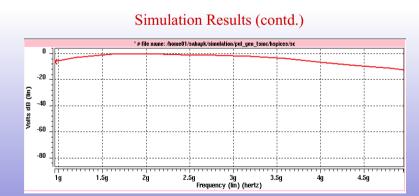

• Monocycle is used as UWB pulse because of no dc component and widebandwidth.

• Halfpower bandwidth is about 116% of monocycle center frequency.

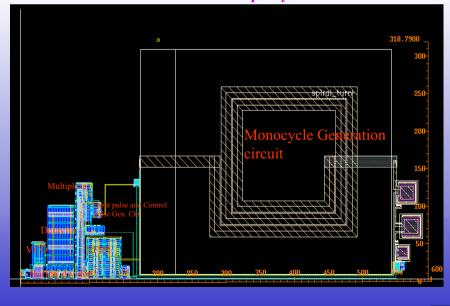

## Transmitter Chip Layout

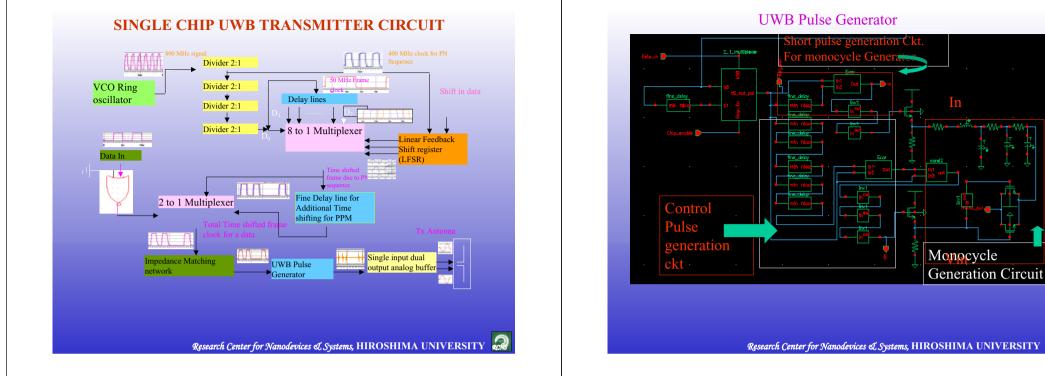

## CIRCUIT DESCRIPTION

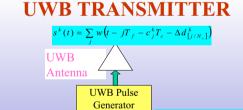

- Five stage current straved inverter with transmission gate at each stage in series are used to form a voltage controlled ring oscillator to produce frame clock via divider circuit.

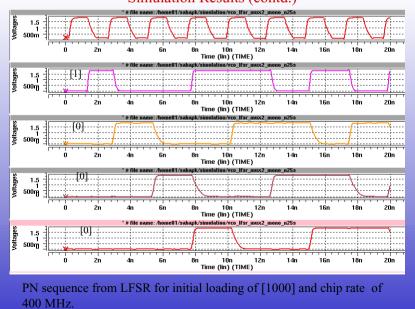

- Linear feed back shift register is implemented using clock controlled D-type flipflop with Exclusive-or (EXOR) as Feedback logic for PN sequence generation.

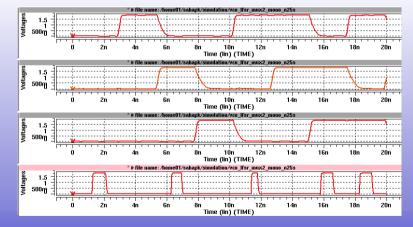

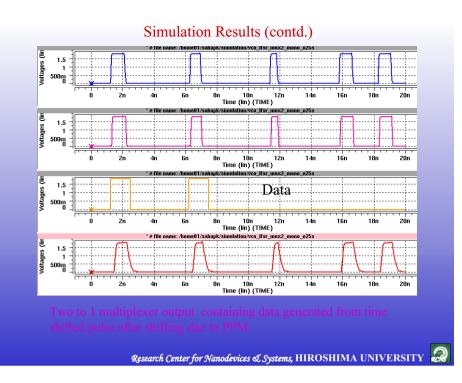

- Eight to 1 multiplexer is implemented using NAND and NOR gate to select time shifted frame in accordence with PN sequence.

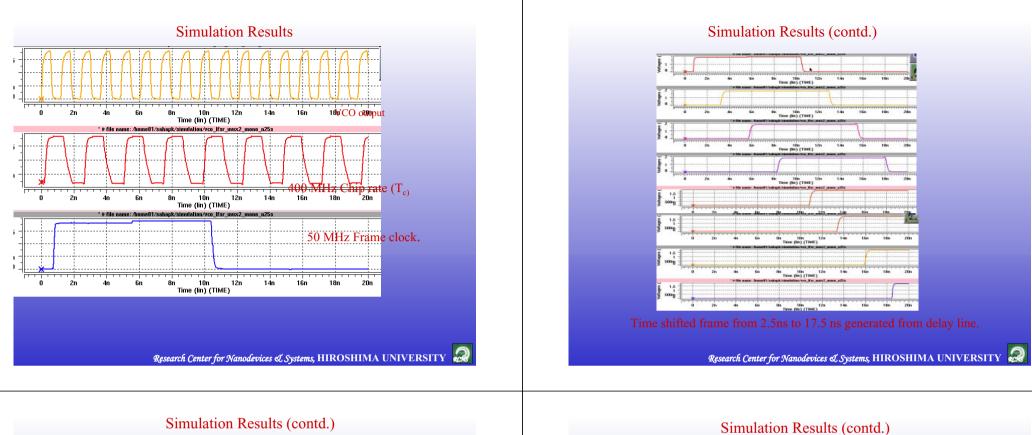

- Time shifted frame is generated using delay generation circuit based on a delay line which consists of a number of buffer stages connected in series.

- The pulse generator circuit which consists of LC oscillator with RC filter produces damped sinusoidal like wave from short pulse (In) generated from the time shifted signal. This signal is then passed through transmission gate which is controlled by control pulse (Vin) of desired width generated from the same time shifted pulse to pass the first cycle of the generated signal at the output.

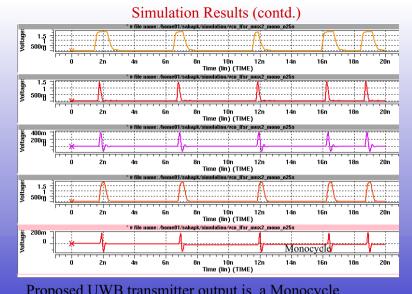

Time shifted signal from Eight to 1 multiplexer output according to PN sequence.

FFT of the generated monocycle pulse having halfpower bandwidth of 2 GHz.

Proposed UWB transmitter output is a Monocycle containing data.

Research Center for Nanodevices & Systems, HIROSHIMA UNIVERSITY 🔬

## CONCLUSION

- Proposed UWB transmitter circuit is almost digital architecture except monocycle pulse generation circuit.

- Monocycle pulse which will contain information can be generated from the time shifted pulse using the current CMOS technology

- Since the monocycle is generated from the time shifted pulse, it is only necessary to keep constant gate delay with any variation of vdd and substrate voltage.

- Monocyle pulse bandwidth can be increased by changing the inductance or capacitance and control pulse width which is equal to monocyle pulse width.