## Design with On-Chip Interconnect Inductance (Invited)

S. Simon Wong, C. Patrick Yue<sup>1</sup>, Richard Chang<sup>2</sup>, Frank O'Mahony<sup>3</sup> Center for Integrated Systems, Stanford University, Stanford CA <sup>1</sup>Carnegie Mellon University, PA <sup>2</sup>Atheros Communications, CA <sup>3</sup>Intel Corporation, OR

#### Abstract

The detrimental effects of interconnect inductance on signal propagation have been widely discussed. This papers describes innovative design concepts that utilize the interconnect inductance to benefit the design of high-speed circuits. Specific examples are illustrated.

#### I. Introduction

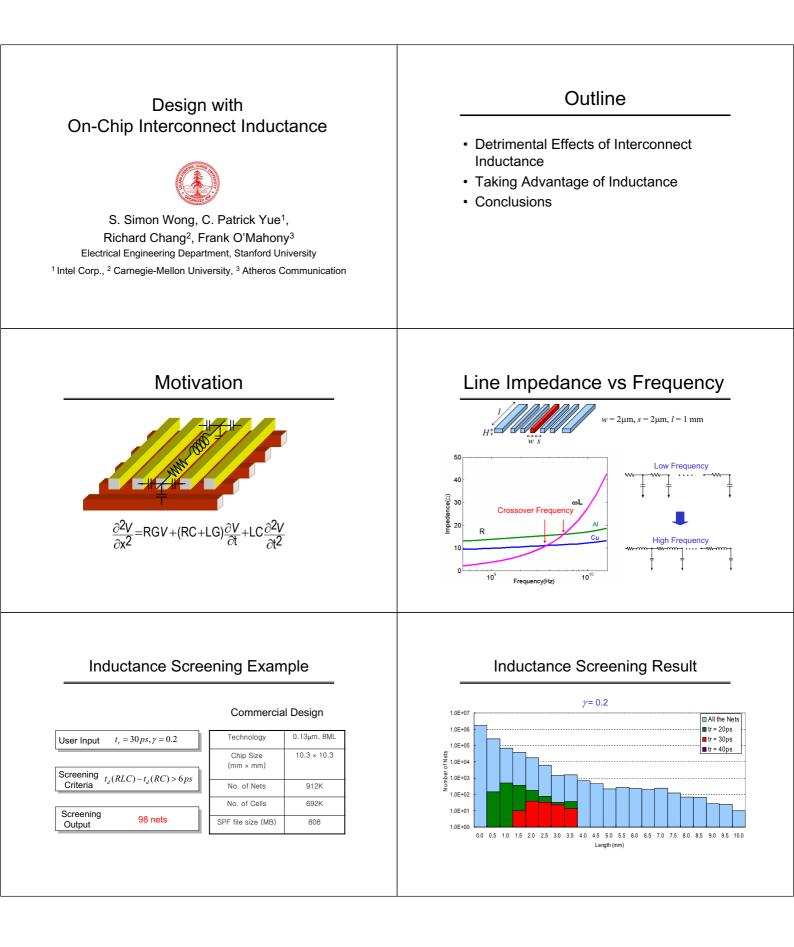

As the operational frequency of an integrated circuit increases beyond GHz, the inductive impedance associate with an on-chip wire becomes comparable or dominant over the resistive component. This could result in additional signal distortion, propagation delay, and cross-talk noise [1, 2]. Hence, the general belief is that inductance, L, is detrimental to interconnect performance, and should be minimized.

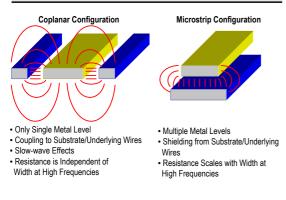

Although the extraction of L associated with a wire randomly placed in a chip is complicated by many factors [3]. L can be controlled if there is a dedicated current return path as in co-planar strip line, or micro-strip line. In such an environment, the wire L can actually provide a new design dimension. This paper describes specific examples of applying wire L in high-speed circuits.

# II. Near Speed-of-Light Propagation of Electrical Signal

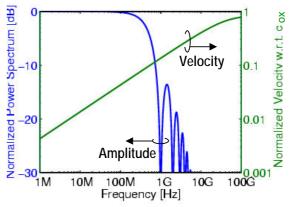

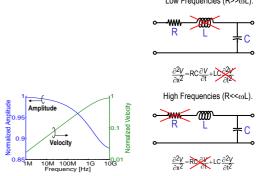

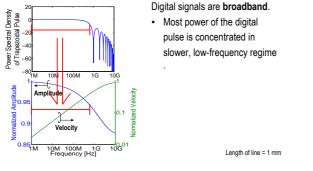

As a digital signal propagates down a long wire, the quality of the signal is degraded resulting in excessive delay or inter-symbol interference. To understand the reasons, the power spectral density of a 500 ps digital pulse is compared with the intrinsic frequency characteristics of a minimum-sized wire in Fig. 1. The digital signal is broadband in nature, while the wire characteristic changes dramatically over this frequency band. At lower frequencies, the wire behaves as a distributed R-C network. In this regime, signals travel very slowly by diffusion and undergo frequency dispersion. As the frequency increases, L begins to dominate over R, and the wire behaves more as a L-C waveguide. The high-frequency L-C regime allows for propagation of an electromagnetic wave; consequently,

the peak velocity is the speed-of-light in the dielectric surrounding the wire.

Figure 1 – Spectral power density of a typical digital pulse, and the signal propagation velocity versus frequency along a minimum-sized wire.

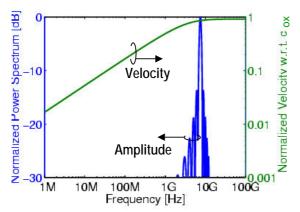

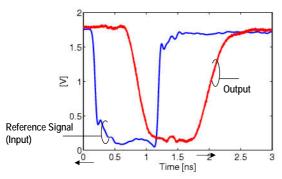

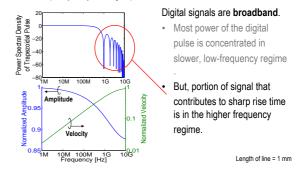

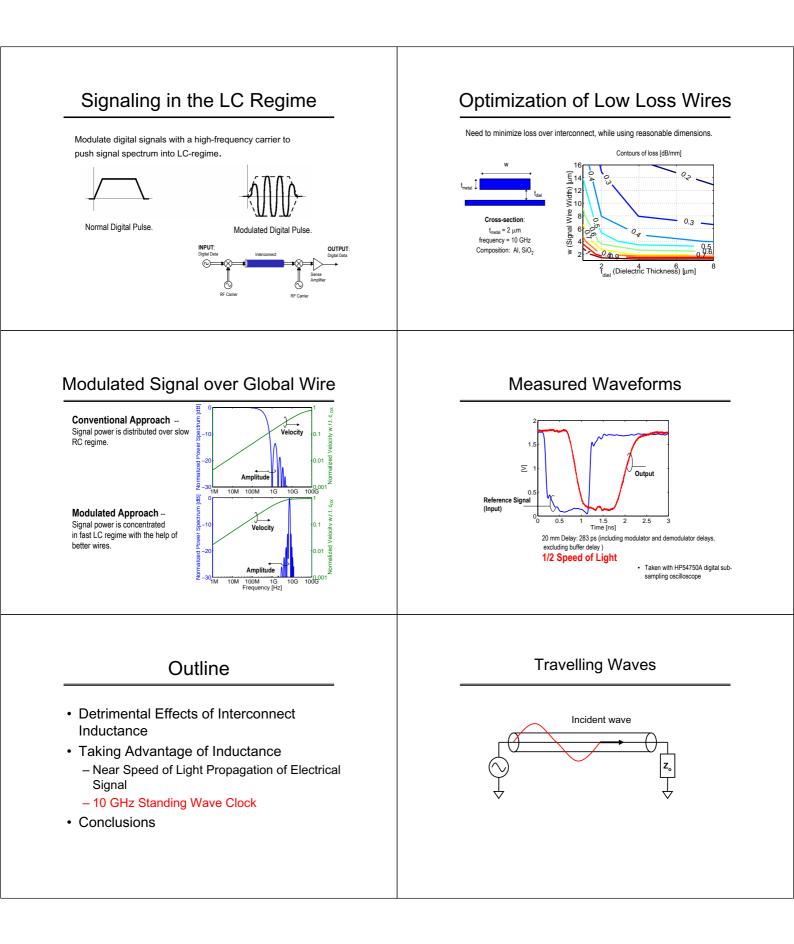

Fig. 1 suggests that a high-speed system can be built by taking advantage of the wave nature of wire [4]. Firstly, it is necessary to eliminate the low-frequency portion of the signal that lags behind. This can be achieved by modulating the digital data with a sufficiently high-frequency carrier, and as a result, concentrating all the signal power in the L-C regime. Secondly, the crossover frequency between the R-C and L-C regimes can be shifted into the single GHz range by explicitly emphasizing L and reducing R. In this frequency range, simple RF circuits can be designed to transmit and receive these modulated signals. Fig. 2 illustrates the impact of using modulated signaling in combination with an optimized low-loss wire to support high-speed transmission. The signal spectral components now lie predominantly in the high-speed L-C regime. This system has been demonstrated in a TSMC 0.18-µm CMOS technology with six levels of Al/Cu wiring and SiO<sub>2</sub> dielectric. The transmitter, receiver, and all other components are integrated on-chip. Fig. 3 shows as-measured input and output waveforms propagating over a distance of 2 cm. Excluding the delay needed for driving signals on and off the chip for testing and measurement., an average delay of 283ps is obtained, which corresponds to an effective signal propagation speed of nearly one-half the speed of light in SiO<sub>2</sub>.

Figure 2 – Spectral power density of a modulated digital pulse, and the signal propagation characteristic of an optimized low-loss wire.

Figure 3 – Measured input and output waveforms of the modulated signal transmission system.

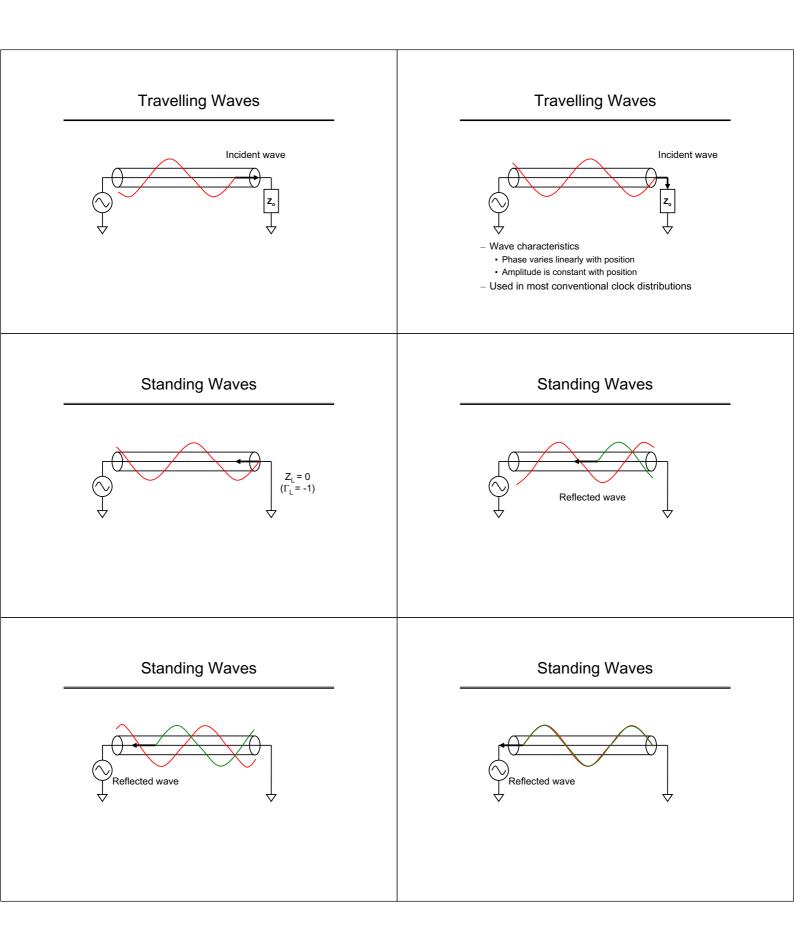

### **III. 10 GHz Standing Wave Clock**

Global clock distribution has become increasingly difficult for multi-GHz microprocessors. Timing uncertainty must reduce with clock period, but skew and jitter for conventional H-trees are proportional to latency, which does not scale with clock period [5].

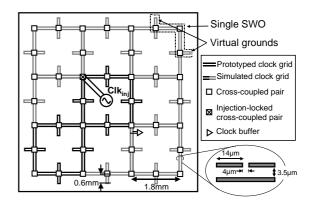

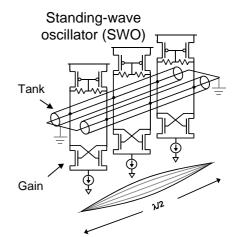

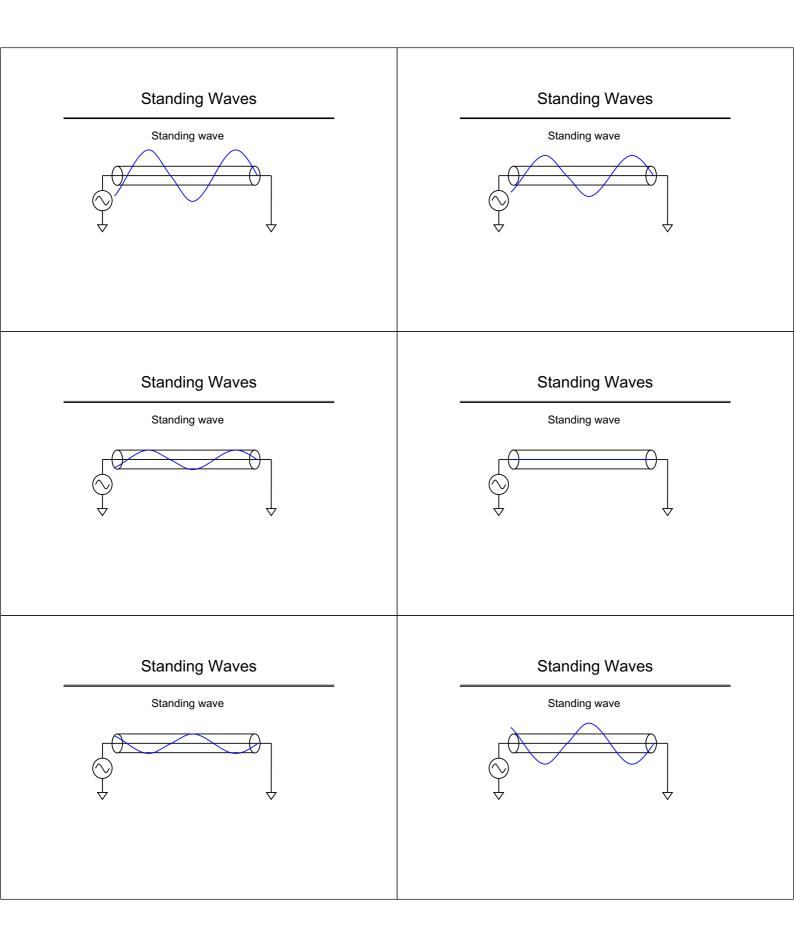

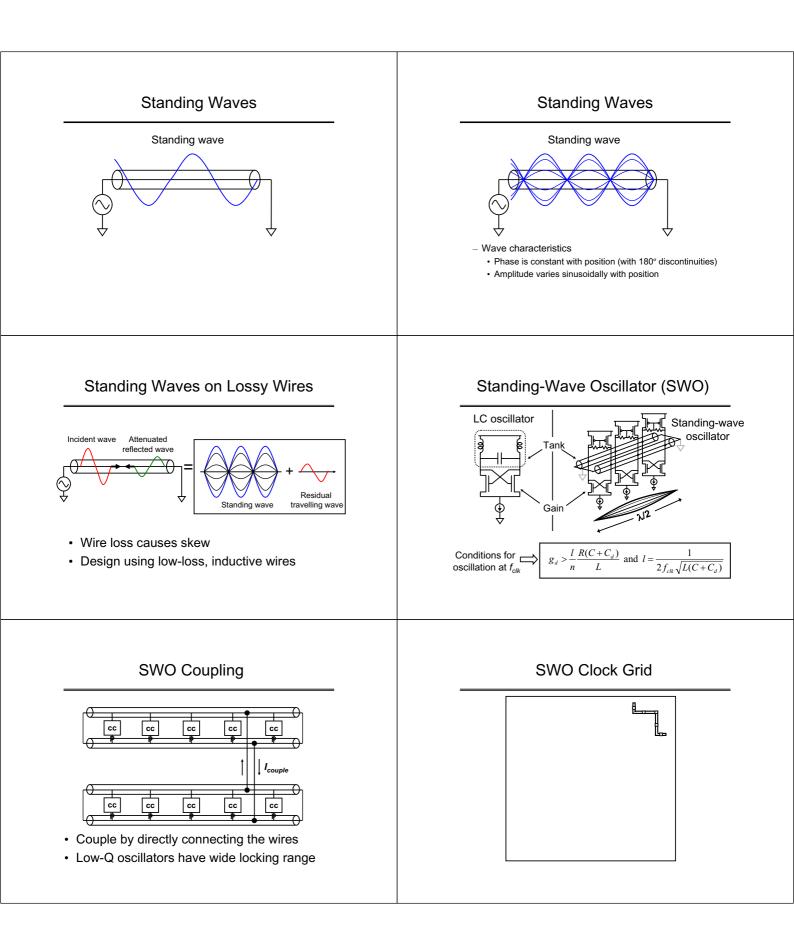

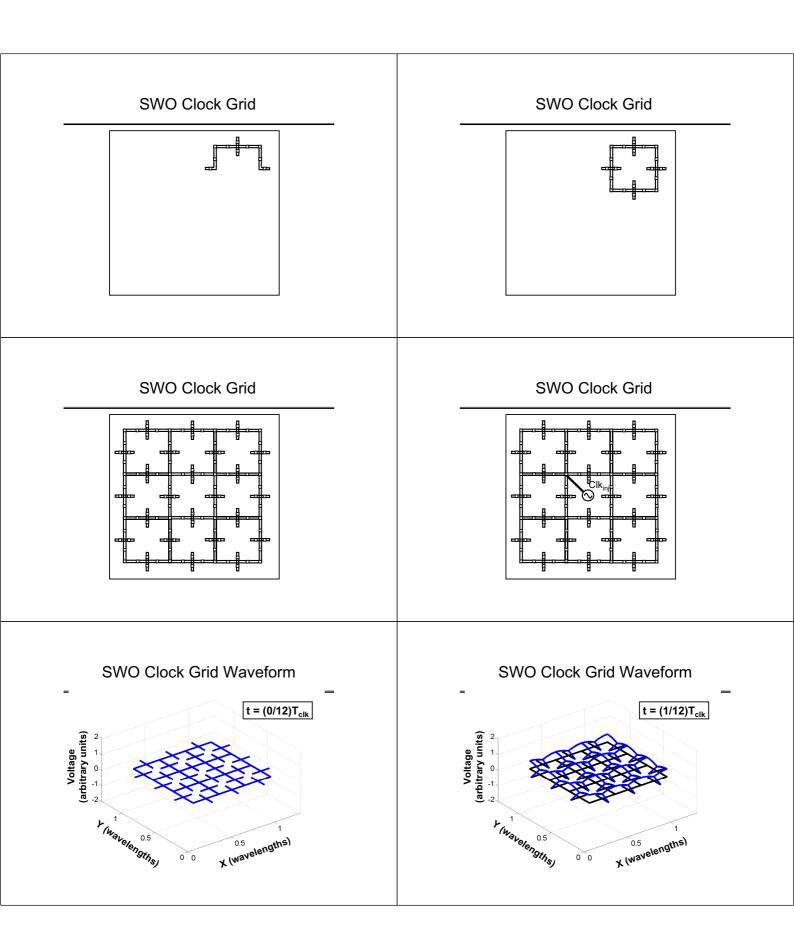

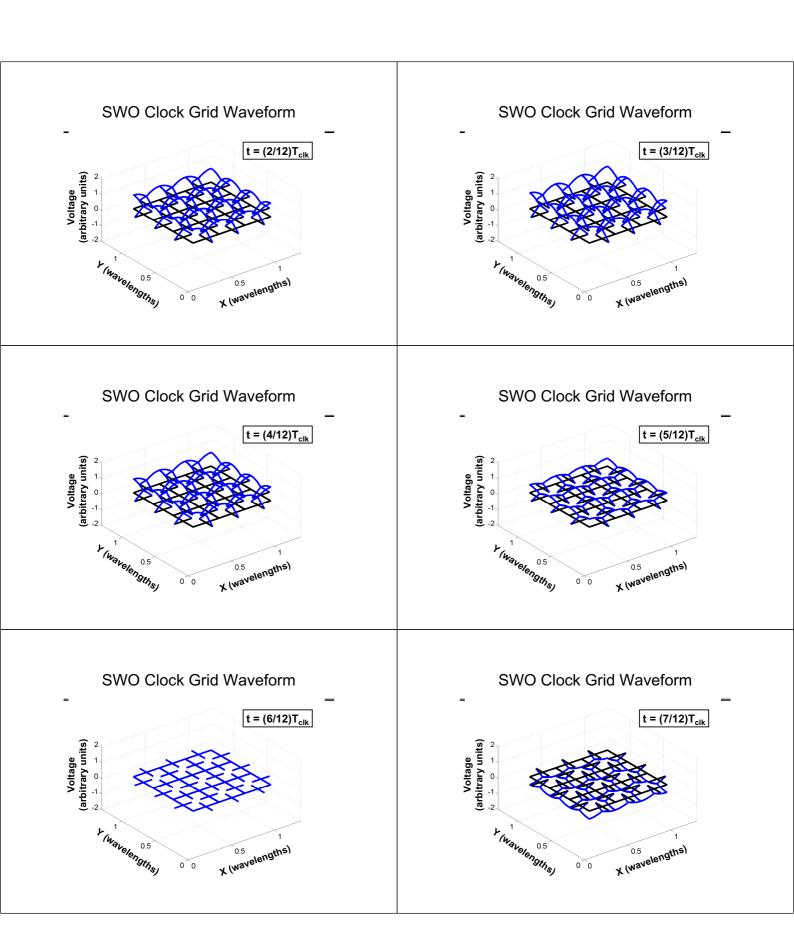

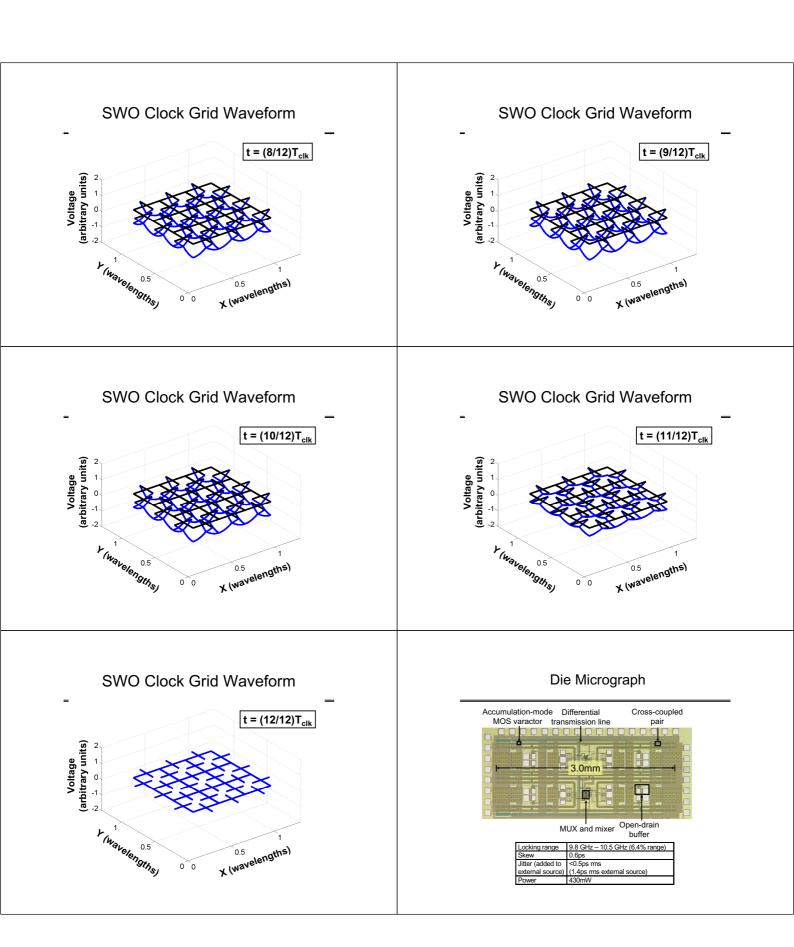

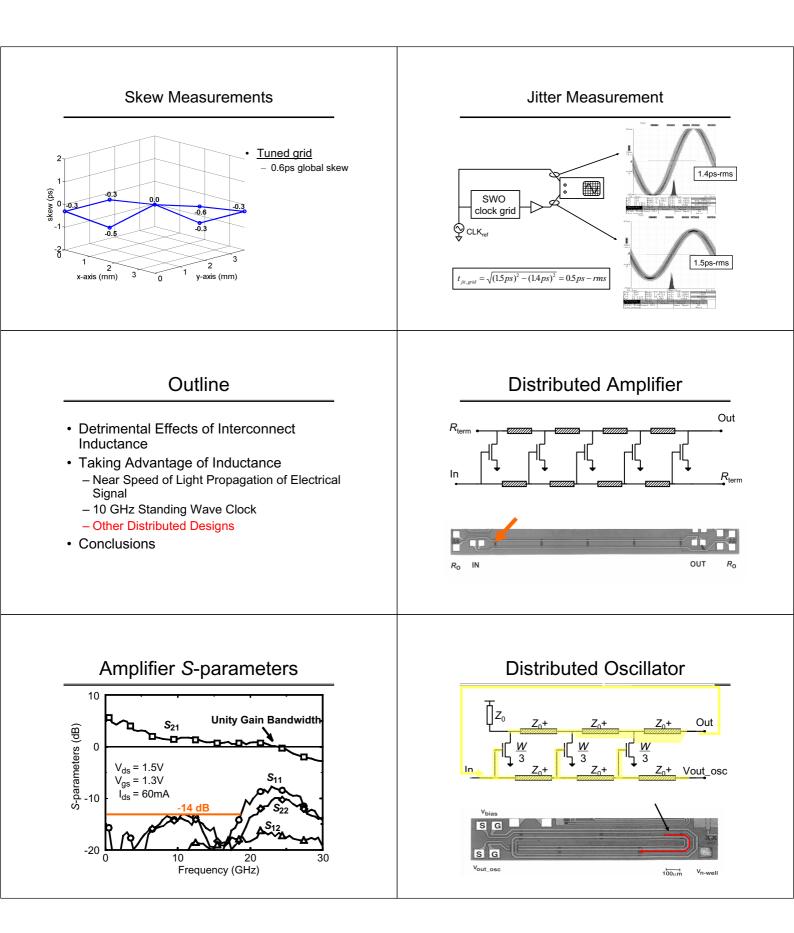

The global clock network in Fig. 4 distributes a 10 GHz clock through a grid of coupled standing-wave oscillators (SWOs) [6]. The SWO, as shown in Fig. 5, is analogous to a differential L-C oscillator where the gain and tank are distributed. These SWOs are coupled together and sustain synchronous, sinusoidal standing waves across the chip. A single clock source coupled into one SWO injection-locks the entire grid. Clock buffers recover a digital clock and drive the local circuits. This coupled SWO clock network has been prototyped in a TSMC 0.18-µm CMOS technology. The test chip integrates eight coupled SWOs. The grid injection locks to an external clock from 9.8 GHz to 10.5 GHz (6.4% locking range). The clock skew and jitter are measured to be less than 1ps.

Figure 4 – 10GHz global clock network with coupled standing wave oscillators.

Figure 5 – Schematic of a standing wave oscillator.

#### 5. Conclusions

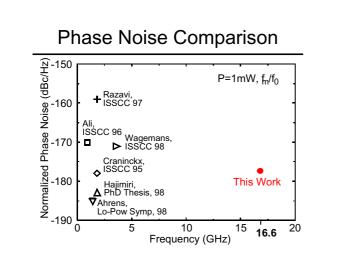

In high frequency operations, wire inductance is not necessary undesirable, but can be exploited for novel design concepts. Other design examples that exploit the distributive behavior of a wire at high frequencies include a 23 GHz distributed amplifier and a 16 GHz distributed oscillator [7].

#### Acknowledgments

The work presented in this paper was partially supported by the MARCO Interconnect Focus Center.

#### References

- [1] Restle, et al, IEEE JSSC, Apr 1998.

- [2] Deutsch, et al., Proc. IEEE, Apr 2001.

- [3] Kim, PhD thesis, Stanford University, 2004.

- [4] Chang, et al, Sym VLSI Circuits, June 2002.

- [5] Restle, et al, IEEE JSSC, May 2001.

- [6] O'Mahony, et al, ISSCC, 2003.

- [7] Kleveland, et al, IEEE JSSC, Oct 2001.

## Outline

- Detrimental Effects of Interconnect Inductance

- Taking Advantage of Inductance

Near Speed of Light Propagation of Electrical Signal

- Conclusions

## **Inductance Definition**

Inductance is a property of a **closed current loop**

# Coplanar versus Microstrip

# Digital Signal over Global Wires

## Digital Signal over Global Wires

Frequency analysis of digital pulse over interconnect.

## Digital Signal over Global Wires

Frequency analysis of digital pulse over interconnect.

## Conclusions

- At high frequencies, interconnect inductance can no longer be ignored

- Extraction of inductance in a typical IC environment is extremely difficult

- Only a small number of interconnects exhibit inductive behavior

- With dedicated return path, interconnect inductance can be controlled & optimized

- Incorporating inductance into distributed designs offer new opportunities