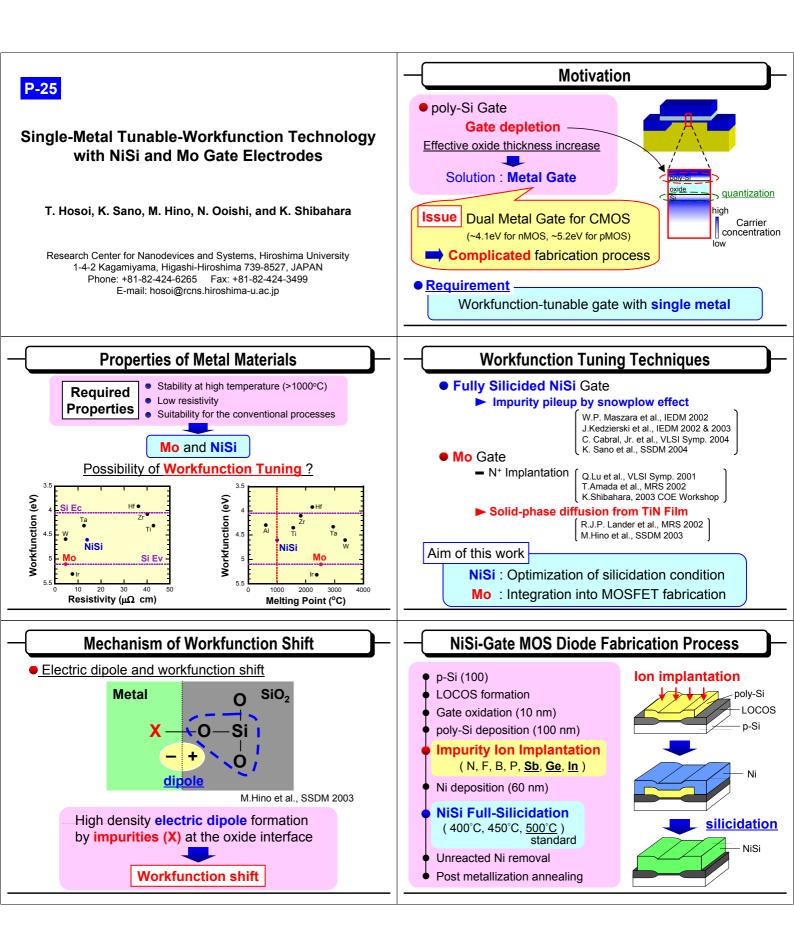

# Single-Metal Tunable-Workfunction Technology with NiSi and Mo Gate Electrode

T. Hosoi, K. Sano, M. Hino, N. Ooishi, and K. Shibahara

Research Center for Nanodevices and Systems, Hiroshima University 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan Phone: +81-82-424-6265, FAX: +81-82-424-3499, E-mail: hosoi@rcns.hiroshima-u.ac.jp

## 1. Introduction

Metal gate technology is expected to solve the problem of poly-Si gate depletion. Since single gate material with dual-workfunction is required for the existing CMOS integration process, workfunction tuning technique for several metals has been extensively investigated. We have reported Mo workfunction tuning with nitrogen introduction at the last COE workshop [1]. This technique still has a trade-off problem between workfunction tunable range and device reliability [2-5]. As an alternative way for the workfunction tuning, we have investigated NiSi. It has been reported that fully silicided NiSi workfunction can be modulated by impurity pileup formed at NiSi/SiO2 interface [6-10]. In this paper, the relationship between impurity depth profile and NiSi workfunction is described. In addition, an application of Nitrogen solid-phase diffusion (N-SPD) to Mo-gate MOSFET process is described.

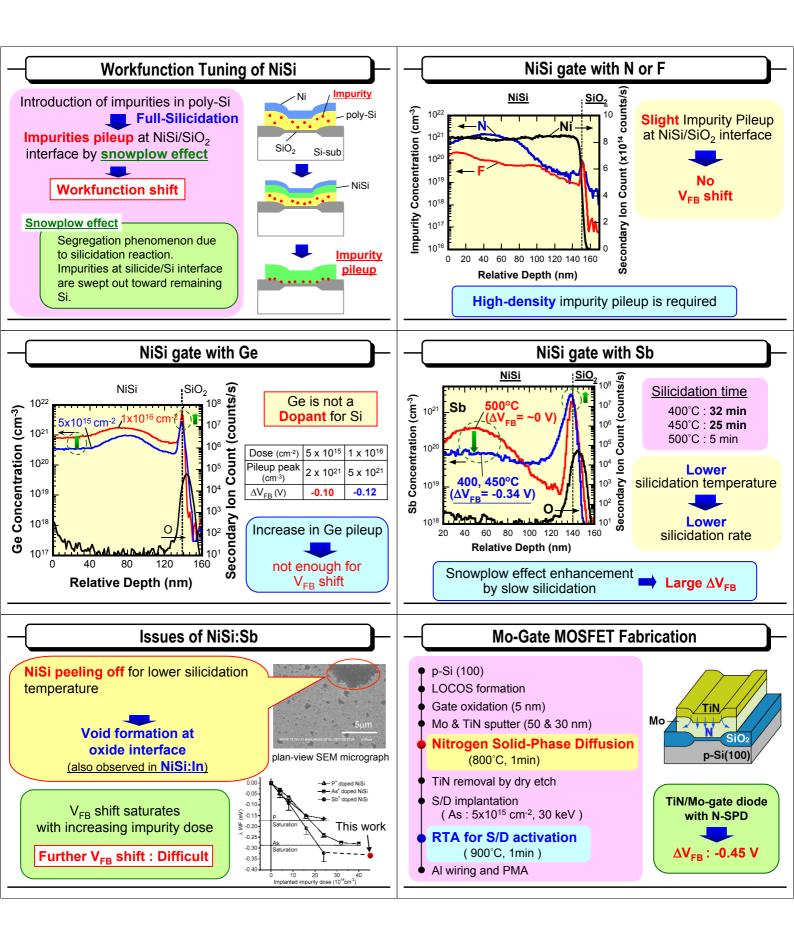

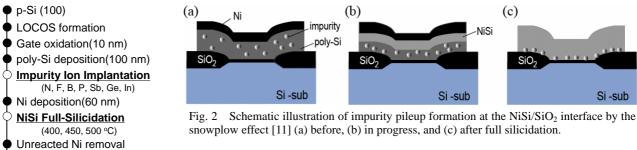

### 2. Workfunction Tuning of NiSi Gate

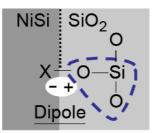

Figure 1 shows the fully silicided NiSi gate MOS diode fabrication process flow. As illustrated in Fig. 2, implanted impurity in poly-Si is swept out toward the NiSi/SiO<sub>2</sub> interface during silicidation by the snowplow effect [11]. It is considered that the workfunction shift originates from electric dipoles formed at the NiSi/SiO<sub>2</sub> interface as shown in Fig. 3 [5]. The previously reported NiSi workfunction shift by using B, P, As, and Sb [6,7] is insufficient for CMOS application (Fig. 4).

In this work, we have investigated the dependence of NiSi workfunction on impurities and silicidation temperature. Silicidation was carried out at 400 °C, 450 °C, or 500 °C by in-situ lamp heating in a vacuum. The detailed conditions of impurity ion implantation and a brief summary of resulting flat-band voltage (V<sub>FB</sub>) shift are listed in Table I. Sb, As, P, B, and Ge yielded flat-band voltage shift, in contrast to the cases of N and F. It is noteworthy that Ge, which is not a dopant for Si, gave rise to V<sub>FB</sub> shift. This indicates that the NiSi workfunction could be modulated more widely with impurities other than dopants.

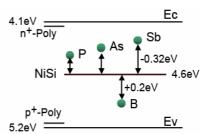

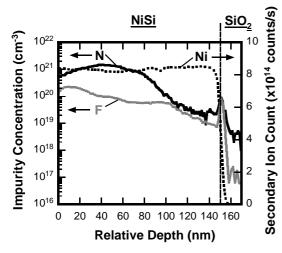

Figure 5 shows the N and F depth profiles after full silicidation at 500 °C. Though the slight impurity pileup at the NiSi/SiO<sub>2</sub> interface is observed, the V<sub>FB</sub> shift was not obtained. Figure 6 shows the Sb depth profiles after full silicidation at various temperatures. The Sb pileup at the NiSi/SiO<sub>2</sub> interface silicided at 450 °C is larger than that at 500 °C. Sb peak formed by the implantation (observed at ~50 nm) vanishes at 450 °C. Lower silicidation temperature leads to lower silicidation rate, and hence increase in swept-out impurities by snowplow effect. The V<sub>FB</sub> shift of -0.34 V was obtained at 400 °C and 450 °C. However, pileup growth results in impurity precipitation at the interface in the end. As shown in Fig. 7, partial film peeling was found after unreacted Ni removal with acid only for

specimens silicided under 450  $^{\circ}$ C [10]. This is attributed to void formation at the NiSi/SiO<sub>2</sub> interface. This void formation was also observed for the sample with In [12]. Though the void formation mechanism is not clear yet, it is assured that impurity concentration in the vicinity of the interface is the key factor. This voiding should be noted as a potential roadblock against practical use of fully silicided NiSi gate.

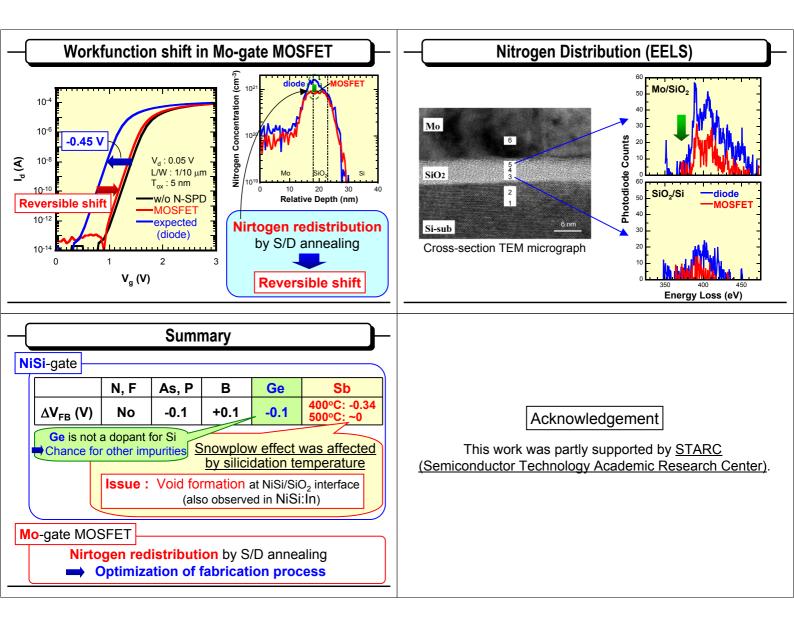

#### 2. Mo-Gate MOSFET

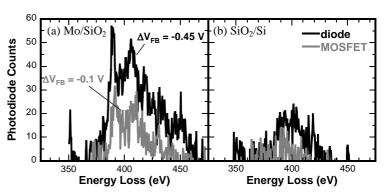

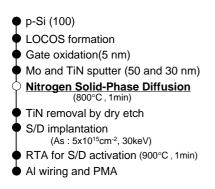

Figure 7 shows the Mo gate nMOSFET fabrication process flow. Though the obtained  $V_{FB}$  shift by N-SPD in MOS diode process was -0.45 V, that in MOSFET process was only -0.1 V, as shown in Fig. 8. Nitrogen EELS signals at the Mo/SiO<sub>2</sub> interface and the SiO<sub>2</sub>/Si interface in both Mo MOS structures were evaluated to discuss the reason why the  $V_{FB}$  shift shrunk (Fig. 9). Nitrogen pileup at the Mo/SiO<sub>2</sub> interface in the diode process reduces by subsequent source and drain (S/D) activation annealing, in other words, by changing fabrication process to MOSFET process. Nitrogen depth profile obtained by back-side SIMS supports this result. These results indicate that the nitrogen pileup reduction due to the nitrogen redistribution in the Mo film causes the reversible workfunction behavior. Therefore, the Mo gate MOSFET fabrication process, especially thermal annealing, should be modified to control the nitrogen redistribution.

#### 4. Summary

Workfunction tuning utilizing impurity pileup at the metal/SiO<sub>2</sub> interface has been investigated. It was found that silicidation temperature was an important factor to enhance the snowplow effect in NiSi. However, problems such as the void formation at the NiSi/SiO<sub>2</sub> interface and the interfacial reaction should be cleared. In the case of Mo-gate MOSFET with N-SPD, a reversible redistribution was observed by subsequent thermal treatment. Thus, the optimization of the fabrication process is required for workfunction tunable Mo-gate MOSFET.

#### Acknowledgements

Part of this work was supported by the Semiconductor Technology Academic Research Center (STARC).

#### References

- K. Sano *et al.*, Proc. of 2nd Hiroshima Int. Workshop on Nanoelectronics for Terra-Bit Information Processing, 2004.

- [2] P. Ranade et al., Mat. Res. Soc. Proc. 670, K5.2.1(2001).

- [3] T. Amada et al., Mat. Res. Soc. Proc. 716, B7.5.1 (2002).

- [4] R.J.P. Lander et al., Mat. Res. Soc. Proc. 716, B5.1.1 (2002).

- [5] M.Hino et al., Ext. Abstr. SSDM 2003, p. 494.

- [6] J. Kedzierski et al., IEDM Tech. Dig. 2002, p. 247.

- [7] J. Kedzierski et al., IEDM Tech. Dig. 2003, p. 315.

- [8] W.P. Maszara et al., IEDM Tech. Dig. 2002, p. 367.

- [9] C. Cabral, Jr. et al., Proc. on VLSI Tech. Symp. 2004, p. 184.

- [10] K. Sano et al., Ext. Abstr. SSDM 2004, p. 456.

- [11] I. Ohdomari et al., J. Appl. Phys. 56, p. 2725 (1984).

- [12] K. Sano et al., submitted to Jpn. J. Appl. Phys.

Fig. 1 Fabrication process flow of fully silicided NiSi gate MOS diodes.

Table I Impurity implantation conditions and resulting  $V_{FB}$  shift. Standard silicidation temperature was 500 °C.

|    | Dose (cm <sup>-2</sup> ) | Energy (KeV) | $\Delta V_{FB}(V)$ |

|----|--------------------------|--------------|--------------------|

| N  | 5.0 x 10 <sup>15</sup>   | 10           | ~ 0                |

| F  | 2.5 x 10 <sup>15</sup>   | 10           | ~ 0                |

| В  | 1.0 x 10 <sup>15</sup>   | 5            | +0.1               |

| Р  | 5.0 x 10 <sup>15</sup>   | 15           | -0.1               |

| Sb | 5.0 x 10 <sup>15</sup>   | 30           | -0.3               |

| Ge | 5.0 x 10 <sup>15</sup>   | 30           | -0.1               |

| In | 5.0 x 10 <sup>15</sup>   | 30           | -0.1 ?             |

Fig. 3 Electric dipole model to explain workfunction shift at the NiSi/SiO2 interfaces [5]. X stands for an impurity atom.

(c)

SiO

Si-sub

Fig. 4 NiSi workfunction tunable range. Drawn based on the data reported by Kedzierski et al. [6,7].

Fig. 6 Sb depth profiles measured by back-side SIMS. Lower silicidation temperature leads to a significant snowplow effect, resulting in larger V<sub>FB</sub> shift.

Fig. 7 Plan-view SEM micrograph of NiSi gate with Sb silicided at 450 °C. Partial NiSi peeling off was found after unreacted Ni removal process.

Fig. 9 Nitrogen EELS signals at (a) the Mo/SiO<sub>2</sub> interface and (b) the SiO<sub>2</sub>/Si interface. In MOSFET process, S/D activation annealing reduces the nitrogen pileup formed by N-SPD, resulting in the less V<sub>FB</sub> shift.

Fig. 5 N and F depth profiles measured by back-side SIMS. The slight impurity pileup at the NiSi/SiO2 interface resulted in no V<sub>FB</sub> shift.

Fig. 8 Fabrication process flow of Mo gate nMOSFETs with N-SPD.