# Interface Trap Generation on MOSFETs with Thin SiO<sub>2</sub> and Plasma-Nitrided SiO<sub>2</sub> Gate Dielectrics under Static and Dynamic Stresses

Shiyang Zhu, Anri Nakajima, Takuo Ohashi \* and Hideharu Miyake \* Research Center for Nanodevices and Systems, Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan \* Elpida Memory, Inc., 1120 Shimokuzawa, Sagamihara, Kanagawa, 229-1198, Japan Phone: 81-82-424-6274, Fax: 81-82-422-7185, Email: nakajima@sxsys.hiroshima-u.ac.jp

#### 1. Introduction

Interface trap and bulk charge generations under both static and dynamic oxide field stresses in MOSFETs constitute a major device reliability concern and have attracted much research interest [1]-[4]. However, the mechanism has not been clearly understood and there are controversies even in the observed phenomena. On the other hand, nitrided SiO<sub>2</sub> has been widely used as gate oxide in modern VLSI, while the effect of nitrogen on the device reliability is still not clear. Here, N-MOSFETs with different nitrided gate oxide were systematically studied under static and dynamic (both bipolar and unipolar) stresses in a wide frequency range between 1 and 10<sup>7</sup> Hz.

#### 2. Devices and Measurement

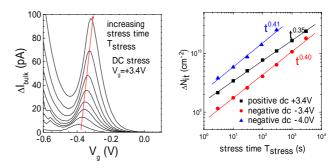

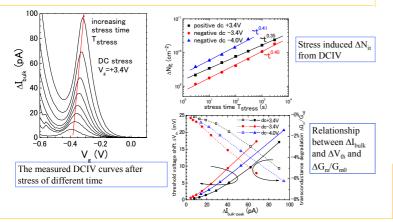

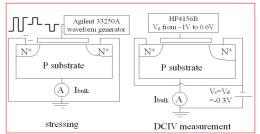

The devices were standard LDD poly-Si gate n-channel MOSFETs with base SiO<sub>2</sub> thickness of 3.48nm, and nitrogen concentration of 0%, 9%, 11%, 12% introduced by plasma-nitridadtion. EOTs of the devices were 3.48, 3.14, 3.04 and 2.94nm respectively. During stressing, a square waveform with a duty factor of 50% was applied to the gate while the substrate, drain and source were grounded and the substrate current (I<sub>bulk</sub>) was monitored. Before and after stress, devices were measured using a direct-current I-V (DCIV) method [5], where the drain and source connected together and biased at -0.3V, and the substrate grounded, the substrate current (I<sub>DCIV</sub>) was measured as scanning the gate voltage (Vg) from -0.6V to 0.2V.  $I_{DCIV}$  has a peak when the recombination current via the interface traps around the channel reaches a maximum as shown in Fig. 1(a). The height of the current peak above the baseline ( $\Delta I_{\text{bulk-peak}})$  is directly proportional to the interface trap density (Nit) approximately, thus the stress-induced interface trap density  $(\Delta N_{it})$  can be extracted. Fig. 1(b) shows the stress time evolution of  $\Delta N_{it}$ under positive or negative dc stress. They obey a typical power-law on time with a fractional exponent of 0.35 to 0.41. A close relationship is also found between the extracted  $\Delta N_{it}$  value and the threshold voltage shift  $(V_{th})$ and the transconductance degradation.

#### 3. Results and Discussion

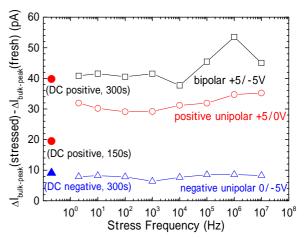

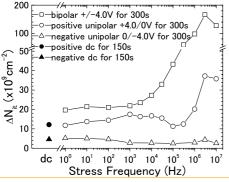

Fig. 2 shows the frequency dependence of the interface trap generation under bipolar and unipolar (both positive and negative) FN stresses of the pure SiO<sub>2</sub> n-MOSFETs, as well as under positive and negative dc stresses. The magnitude of applied voltage keeps the same (5 V) for

**Fig. 1** (a) The measured DCIV curves after stress for 0 to 5000s. (b) The time evolution of the stress induced interface trap density, it obeys a power-law dependence on time.

**Fig. 2** Interface trap generation of the pure  $SiO_2$  n-MOSFETs as a function of stressing frequency after bipolar and unipolar (positive and negative) stresses for 300s, the data of dc stresses are also shown for comparison.

both polarities. Note that different device was tested for every point in Fig. 2, i.e.,  $\Delta I_{bulk-peak}$  of the fresh device was measured first, and it was measured again after stressing for 300s. The increase of  $\Delta I_{bulk-peak}$ , which is directly proportional to the stress-induced interface trap density  $(N_{it})$  in MCR, was obtained by

$\Delta I_{bulk\text{-peak}}(\text{stressed})$  -  $\Delta I_{bulk\text{-peak}}(\text{fresh}).$  In our experiments, the  $\Delta I_{bulk\text{-peak}}(\text{fresh})$  data of all tested devices are between  $0.5 \sim 2.5 pA$ , demonstrating that the interface trap density is well-controlled in mature production technologies. Considering the 50% duty time of the dynamitic stress, data after 150s positive dc stress

are also shown for comparison. It can be seen that bipolar stress has higher interface trap generation than unipolar stresses. This observation is consistent with Refs. [1] and [2] and it has been explained the fact that bipolar stress can produce interface traps for the entire cycle, while unipolar stress produces interface traps for only one-half cycle. In Fig. 2, we really see that the value of bipolar stress is close to the sum of those of positive and negative unipolar stresses in the low frequency region.

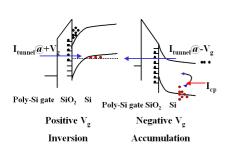

It appears that the interface trap generation under the positive dc or unipolar stress is significantly larger than that under the negative stress with the same magnitude of  $V_{gb}$ . This is because the oxide voltage ( $|V_{ox}|$ ) is different for the same positive and negative gate voltage  $|V_{\text{gb}}|$  due to the flatband voltage ( $V_{FB}$ ) and the surface potential ( $\psi_s$ ). For inversion (positive  $V_{gb}$ ),  $V_{ox} = V_{gb} - V_{FB} - 2\phi_F$ , where  $q\phi_F$  is the energy different between the midgap position and the Fermi level. For accumulation (negative V<sub>gb</sub>), V<sub>ox</sub> is given as:  $V_{ox} = V_{gb} - V_{FB} - (0.56 - \phi_F)$ . Our sample has the values of  $V_{FB}$  and  $\phi_F$  of -1.02eV and 0.47eV respectively. Therefore,  $V_{gb} = -5.0V$  results in  $V_{ox} =$ -4.07V and  $V_{\rm gb} = 4.8$ V gives  $V_{\rm ox} = 4.88$ V. When scaled to the same magnitude of |Vox|, the negative stress generates the interface traps even more effectively than the positive ones [2] (not shown in our figures). For the bipolar stress, Fig. 2 shows that the frequency dependence of interface trap generation can be divided into three regions: (1) for frequency less than about  $10^4$  Hz,  $\Delta N_{it}$  is almost independent of frequency, (2) for frequency between 10<sup>4</sup> to  $10^6$  Hz,  $\Delta N_{it}$  increases with frequency, and (3) for frequency between  $10^6$  to  $10^7$  Hz,  $\Delta N_{it}$  reaches a maximum and decreases with further increasing of frequency. The phenomena of (1) and (2) were also found by Chen et al. [2], while the 3<sup>rd</sup> phenomenon is observed for the first time. For both positive and negative unipolar stresses, no frequency dependency is found.

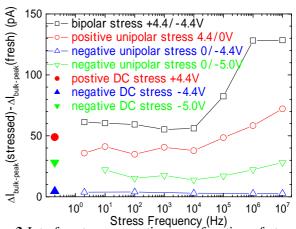

Fig. 3 shows the static and dynamic stress results of the plasma nitrided SiO<sub>2</sub> n-MOSFETs with nitrogen concentration of 12%. The magnitude of the applied V<sub>gb</sub> is reduced to 4.4V due to its smaller EOT and higher gate leakage. The frequency dependence of the interface trap generation under bipolar stress displays similar three regions as in Fig. 2. Moreover, in the case of positive unipolar stress, the increase of N<sub>it</sub> at frequency larger than 10<sup>4</sup> Hz is also observed, but with weaker frequency dependence than that under bipolar stress. For the negative unipolar case,  $V_{gb} = -4.4V$  results in very small  $\Delta N_{it}$ , and no frequency dependence. With increasing  $V_{\rm gb}$  to -5.0V,  $\Delta N_{it}$  increases and very weak frequency dependence also appears in the high frequency region. It implies that all dynamic stresses (bipolar, positive and negative unipolar) have the similar frequency dependence behavior, and the strength of the dependence at the high frequency region (between 10<sup>4</sup> to 10<sup>6</sup> Hz) may be correlated to the stress type and/or the magnitude of  $\Delta N_{it}$  itself.

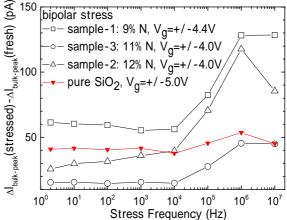

To confirm the above finding, other two plasma nitrided SiO<sub>2</sub> samples with nitrogen concentration of 9% and 11%

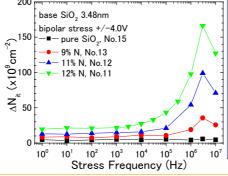

were also tested. Fig. 4 shows their results. All samples show the similar behavior of frequency dependence. At the high frequency region between  $10^4$  and  $10^6$  Hz, the plasma nitrided SiO<sub>2</sub> samples have stronger frequency dependence than the pure SiO<sub>2</sub> counterpart.

**Fig. 3** Interface trap generation as a function of stressing frequency at dynamic stresses for the nitrided SiO<sub>2</sub> sample. The values after static dc stresses are also shown. The stress time keeps 300s for all devices.

**Fig. 4** Frequency dependence of the interface trap generation under the bipolar stress for various samples.

#### 4. Conclusion

The frequency dependence of interface trap generation under dynamic (both positive and negative) and dc oxide field stress were studied systematically. A model is proposed to explain it. Nitrogen incorporation increases both the interface trap generation and its frequency dependence.

#### **References:**

- [1] E. Rosenbaum, et al., IEEE Trans. Electron Devices, 40, p.2287 (1993)

- [2] T. P. Chen, et al., IEEE Trans. Electron Devices, 45, p.1920 (1998)

- [3] B. Wang, et al., IEEE Electron Device Lett., 22, p.224 (2001)

- [4] R. Rodriguez, et al., IEEE Trans. Electron Devices, 45, p.881 (1998)

- [5] J. Cai, et al., IEEE Electron Device Lett., 20, p.60 (1999)

# Interface Trap Generation on MOSFETs with Thin SiO<sub>2</sub> and Plasma-Nitrided SiO<sub>2</sub> Gate Dielectrics under Static and Dynamic Stresses

Shiyang Zhu, Anri Nakajima

Research Center for Nanodevices and Systems, Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan

#### Takuo Ohashi, Hideharu Miyake

Elpida Memory, Inc., 1120 Shimokuzawa, Sagamihara, Kanagawa, 229-1198, Japan

#### The aims of this study:

- Interface trap generation (N<sub>it</sub>) under dynamic oxide field stresses shows different behaviors as that under static stress.

- The reported data in literature are inconsistent, therefore, systematical studies are necessary.

#### The devices used in this study:

• Standard n-MOSFETs with LDD, poly-Si gate and ultra-thin plasma-nitrided SiO<sub>2</sub> gate dielectric with base thickness of **3.48nm** and N concentration of 0%, 9%, 11%, 12%.

#### Stress and measurement setup:

- Stress: bipolar, unipolar (positive and negative) and static stresses are applied on gate  $V_{\rm g}$  while other electrodes are grounded.

- Measurement: direct current I-V (DCIV) method is used to extract N<sub>it</sub>

Interface trap density  $N_{ii}$  can be extracted from the peak of DCIV curves

$$I_{P-DCIV}(V_e, N_{it}) = \frac{qN_{it}An_ic_s}{2} \left(\exp(qV_e/nkT) - 1\right)$$

## Frequency dependence of N<sub>it</sub> at different kinds of stress

Frequency dependence of N<sub>it</sub> at bipolar stress for devices with different nitrogen concentrations

### New findings of the stress-induced interface traps

• For bipolar stress, the frequency dependence divided three parts :

(1)f < 10<sup>4</sup> Hz, independent on frequency;

$\Delta N_{it}$  (bipolar) =  $\Delta N_{it}$  (positive unipolar) +  $\Delta N_{it}$  (negative unipolar) =  $\Delta N_{it}$  (positive static) +  $\Delta N_{it}$  (negative static)

(2)  $10^4$  Hz < f <  $10^6$  Hz, increase with frequency;

(3) at  $f > 10^6$  Hz,  $\Delta N_{it}$  saturates or decreases at higher frequency.

- For **unipolar** stress, the frequency dependency is weak.

- The higher N concentration results in larger  $\Delta N_{it}$  and stronger frequency dependency

- Higher  $V_g$  results in larger  $\Delta N_{it}$  and stronger frequency dependency.

#### Explanation --- Charge pumping current induced interface traps

#### The framework of interface trap generation The energetic species (electrons, holes, H<sup>+</sup> etc.)

- (1) Carriers are tunneled in oxide

- (2) Energy is supplied by diffusion in oxide or recombination

- Precursors of interface trap (such as Si-H bonds) are broken.

- Diffusion of released species to avoid initial recovery.

### New traps were created

#### The charge pumping current

- $\bullet$   $I_{CP}\left(\sim f\right)$  may also contribute energy to species to break the bonds

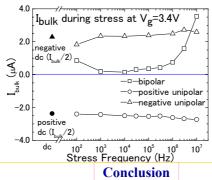

- $\bullet$   $I_{\text{CP}}$  can be measured from  $I_{\text{bulk}}$  during stress.

- $\bullet$   $I_{bulk} = averaged I_{tunnel} + I_{CP}$

- $\bullet$   $I_{CP}$  dominates at  $f\!>10^4$  Hz and  $I_{CP}$  increases with f.

- I<sub>CP</sub> is small for unipolar stresses

#### The saturation of $\Delta N_{it}$ at the MHz region

• CP current: the recombination of trapped electrons and holes from the bulk around the interface ( $I_{\text{CP-FS}}$ ) and near interface ( $I_{\text{CP-SS}}$ ).

$$I_{CP} = I_{CP-FS}(fast\_states) + I_{CP-SS}(slow\_states)$$

$$\propto \Delta F(fast\_states) \cdot f + \Delta F(slow\_states) \cdot f$$

$\Delta F$ : the filling factor,  $\Delta F$ (fast\_states)  $\approx 1$  at  $1 \sim 10^7 Hz$

$\Delta$ F(slow states) become to reduce at f > 10<sup>6</sup>Hz

$I_{CP-SS}$  (slow\_states) may create  $\Delta N_{it}$  more effectively.

- **1** New founding: the frequency dependent interface trap generation shows different behavior at different frequency region.

- **②** New model: Charge pumping current ( $I_{CP}$ ) was introduced to explained the frequency dependency of  $\Delta N_{it}$ . The saturation of  $\Delta N_{it}$  at the MHz frequency implies that the slow state charge pumping current ( $I_{CP-SS}$ ) dominates the generation of  $\Delta N_{it}$ .

- $\ensuremath{\mathfrak{J}}$  Higher N concentration results in larger  $\Delta N_{it}$  and stronger frequency dependence