## Room Temperature Operation of an Exclusive-OR Circuit Using a Highly-Doped Si Single-Electron Transistor

Tetsuya Kitade, Kensaku Ohkura and Anri Nakajima

Research Center for Nanodevices and Systems, Hiroshima University 1-4-2 Kagamiyama, Higashi-Hiroshima, Hiroshima 739-8527, Japan Phone: +81-82-424-6265, Fax: +81-82-422-7185, E-mail: kitade@sxsys.hiroshima-u.ac.jp

#### 1. Introduction

Single-electron devices utilizing the Coulomb blockade effect are promising for use as the basic elements of future low-power and high-density integrated circuits.<sup>1-4</sup> To develop these devices into commercial products, a room temperature operation capability and a Si construct are necessary.

Single-electron transistor (SET) applications to logic circuits need to have more advanced functional features than the features which conventional metal-oxide-semiconductor (MOS) have. circuits Takahashi et al.<sup>5</sup> reported an exclusive-OR (XOR) circuit operation using a Si SET fabricated by a pattern-dependent oxidation at 40 K. They utilized the Coulomb oscillation and the ability of a SET to contain several gate electrodes. Saitoh et al.<sup>6</sup> reported an XOR circuit operation using a point-contact channel single-hole transistor with a single dot at room temperature. Recently we have fabricated highly-doped Si SET with a series of geometrically defined multiple islands and multiple side gates.<sup>7</sup> Highly-doped SETs have the advantage of being easy to fabricate because it requires only one electron beam (EB) mask to form Coulomb islands and the double side gates. Moreover, SETs with serially connected multiple Coulomb islands have the advantage both for high temperature operation<sup>8</sup> and the suppression of cotunneling. Using the SET, we have also reported an exclusive-Not-OR (EXNOR) circuit operation at 77 K using this SET.<sup>9</sup>

This time, a large peak-to-valley current ratio (PVCR) of Coulomb oscillation was observed even at room temperature in the SET with the multiple Coulomb islands. Therefore, in this study, using the room temperature characteristics, we report an XOR operation at room temperature. Since the SET with multiple gates reduces the number of required transistors for the logic circuit compared with using conventional complementary MOS transistors, the room temperature operation and easy fabrication of the circuit should open up the development of SET logic circuits.

#### 2. Device Fabrication

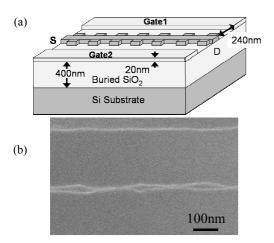

We fabricated a one-dimensional regular array of 22 nanoscale islands in an SOI layer using EB lithography. Figure 1(a) shows the schematic of the SET. Multiple gates (indicated as Gate1 and Gate2) were formed at both sides of the channel wire. Doping of the top Si layer was carried out by POCl<sub>3</sub> diffusion at 800 °C. The doping level was

about 2 x  $10^{19}$  cm<sup>-3</sup>. After dry etching by using an electron cyclotron resonance etcher with the resist pattern as a mask, subsequent isotropic wet etching in a NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O solution was conducted to reduce the dimensions of the device.<sup>10</sup> The final thickness of the top Si layer was about 20 nm. After the wet etching [Fig.1(b)], the width of the island and that of the region between adjacent islands were about 20 and 10 nm, respectively. The distance between the centers of adjacent islands was 250 nm and the length of the narrow channel wire region (~10 nm) between adjacent islands was about 50-100 nm. The separation between the channel wire and the side gates was 240 nm.

#### 3. Coulomb oscillation of SET with multiple islands

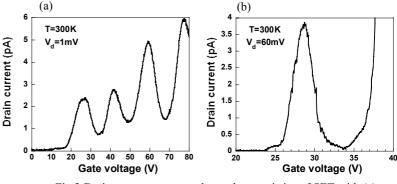

Figure 2 shows Coulomb oscillations of SET with a single island (a) and with 22 islands (b) at room temperature. The maximum PVCR observed is 3.5 in SET with a single island (a) and 77 with 22 islands. We found a tendency that SETs with multiple islands have larger PVCR than SETs with a single island. Large PVCR is advantageous to circuit operations.

#### 4. Application to XOR operation at room temperature

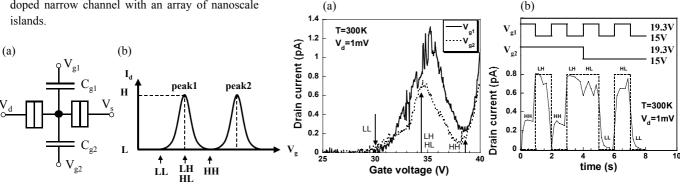

The SET with multiple gates can operate as an XOR by utilizing the oscillatory drain current (I<sub>d</sub>) characteristics (Coulomb oscillation). Figure 3(a) shows an equivalent circuit of our SET with multiple (double) gates. Figure 3(b) shows operation principle of the SET with multiple gates. The I<sub>d</sub> oscillation is determined by the sum of the products of each gate capacitance (C<sub>gi</sub>) and gate voltage (V<sub>gi</sub>). When C<sub>g1</sub> is equal to C<sub>g2</sub>, I<sub>d</sub> is simply a function of the sum of V<sub>gi</sub>.

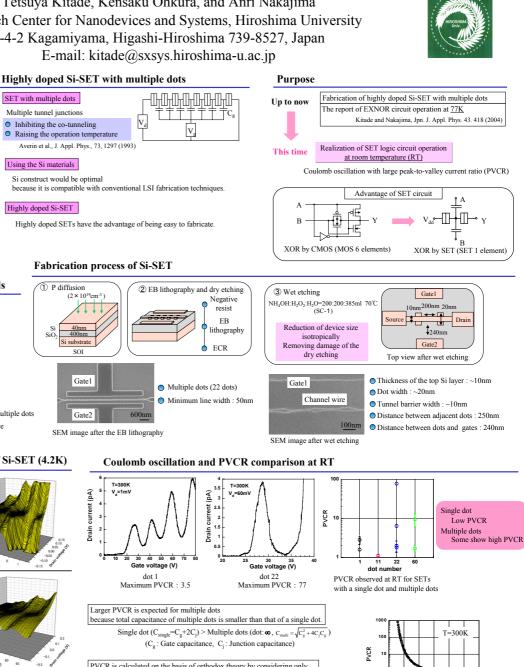

Figure 4(a) shows the  $I_d$  characteristics of our SET with 22 islands at room temperature as a function of  $V_{g1}$  or  $V_{g2}$ . Here, the voltage of only one of the side gates was swept with the other side gate voltage kept 0 V. As seen in the figure, the characteristics with  $V_{g1}$  are nearly equal to those with  $V_{g2}$ . This indicates that  $C_{g1}$  almost equals  $C_{g2}$ , which enables an easy application of our SET to the XOR logic circuit. The  $I_d$  peak appears when the gate voltage is about 34.3 V, and the  $I_d$  valley appears when the gate voltage is about 38.6 V. We chose the low (L) and high (H) input voltages for one side gate to be 15 and 19.3 V, respectively, for the XOR operation. Then, the sum of the voltages of the two side gates becomes 30 and 38.6 V for the LL and HH input gate voltage states, respectively. For the LH and HL input states, the sum becomes 34.3 V.

Figure 4(b) shows the  $I_d$  switching in response to the

switching of the two input gate voltages between 15 V (L) and 19.3 V (H) at room temperature. When the input voltages are the LL and HH states, the output  $I_d$  is L (smaller than 0.3 pA). When the input voltages are the LH and HL states, the output  $I_d$  is H (higher than 0.6 pA). These results demonstrate a successful XOR operation in our SET circuit.

#### 5. Summary

We fabricated a highly-doped Si SET with multiple islands and multiple side gates. The SET exhibited Coulomb oscillation with large PVCR at room temperature. We applied the Coulomb oscillation and the multiple gate input characteristics to an XOR operation and achieved a successful  $I_d$  switching at room temperature. Using an SET with multiple gates requires having fewer transistors in a logic circuit compared with a circuit composed of conventional CMOS transistors. Besides that advanced functional feature, easy fabrication and room temperature operation of our proposed circuit prove the feasibility of practical SET logic circuits.

#### References

- [1] J. R. Tucker, J. Appl. Phys. 72, 4399 (1992).

- [2] Y. Takahashi, M. Nagase, H. Namatsu, K. Kurihara, K. Iwadate, Y. Nakajima, S. Horiguchi, K. Murase and M. Tabe, 1994 International Electron Devices Meeting, p. 938 (1994).

- [3] A. Nakajima, T. Futatsugi, K. Kosemura, T. Fukano and N. Yokoyama, Appl. Phys. Lett. 71, 353 (1997).

- [4] T. Sakamoto, H. Kawaura and T. Baba, Appl. Phys. Lett. 72, 795 (1998).

- [5] Y. Takahashi, A. Fujiwara, K. Yamazaki, H. Namatsu, K. Kurihara and K. Murase, Appl. Phys. Lett. 76, 637 (2000).

- [6] M. Saitoh and T. Hiramoto, 2003 International Electron Devices Meeting, p. 753, (2003).

- [7] T. Kitade, K. Ohkura and A. Nakajima, 2003 international conference on Solid-State Device and Materials, p.584 (2003).

- [8] A. Nakajima, Y. Ito and S. Yokoyama, Appl. Phys. Lett. 81, 733 (2002).

- [9] T. Kitade and A. Nakajima, Jpn. J. Appl. Phys. 43, 418 (2004).

- [10] A. Nakajima, H. Aoyama and K. Kawamura, Jpn. J. Appl. Phys. 33, 1796 (1994).

Fig.1 (a) Schematic diagram and (b) SEM image of the SET having double side gates and a highly doped narrow channel with an array of nanoscale islands.

Fig.2 Drain current vs gate voltage characteristics of SET with (a) a single island and (b) 22 islands at room temperature. The observed maximum PVCR is (a) 3.5 and (b) 77.

Fig.3 (a) Equivalent circuit of our SET with double gates.  $C_{gi}$  and  $V_{gi}$  stand for gate capacitance and voltage, respectively.  $V_d$  and  $V_s$  are drain and source voltages.  $V_s$  is grounded. (b) Operation principle of the SET with multiple gates. When the sum of the two input voltages becomes a voltage where peak appears, the drain current (I<sub>d</sub>) increases (high (H) output state). On the other hand, when the sum becomes a voltage where a valley appears, I<sub>d</sub> decreases (low (L) output state).

Fig.4 (a) Drain current ( $I_d$ ) vs gate voltage characteristics of SET with 22 islands at room temperature. The solid and the broken lines are characteristics shown as a function of  $V_{g1}$  and  $V_{g2}$ , respectively. (b) Measured  $I_d$  switching characteristics when the input gate voltages ( $V_{g1}$  and  $V_{g2}$ ) are switched between 15 and 19.3 V at room temperature. Dotted line shows the ideal output current of XOR circuit.

# Room Temperature Operation of an Exclusive-OR Circuit Using a Highly-Doped Si Single-Electron Transistor

Tetsuya Kitade, Kensaku Ohkura, and Anri Nakajima Research Center for Nanodevices and Systems, Hiroshima University 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan E-mail: kitade@sxsys.hiroshima-u.ac.jp

V<sub>d</sub>

SET with multiple dots

Multiple tunnel junctions

Using the Si materials

Highly doped Si-SET

0

Inhibiting the co-tunneling

Raising the operation temperature Averin et al., J. Appl. Phys., 73, 1297 (1993)

Si construct would be optimal

P diffusion

(2×1019cm

40nm

SOI

Gate1

Gate2

600nr

Introduction

Merit

Multiple dots

Feature

Aggressive scaling of MOSFET

The present state of SET

Application of SET

Inverter XOR·EXNOR

400nm Buried SiC

Si substrate

• Using the Silicon-on-insulator (SOI)

• Double (multiple) side gates

The device based on a new operation principle

Low-power consumption

High density integration

Controllability of electron nu

Structure of Si-SET with multiple islands

• Dot, side gate, drain and source fabricated by one mask

The tunnel barriers formed by constrictions of channel wire

10n

One-dimensional regular array of geometrically defined multiple dots

1(H) 0(L

1(H) 1(H)

I,

1 (H)

0 (L)

ĹĹ

2 (HH)

0 (L)

LH HH + XOR

Operation principle of SET with multiple gates

$= C_{g2}$

Equivalent circuit of SET

with double gates

Id oscillation is determined by sum of the gate voltages

$\Delta Q = C_{g1} \Delta V_{g1} + C_{g2} \Delta V_{g2}$

$=C(\Delta V_{g1}+\Delta V_{g2})$

dot

Input 2  $V_{g2}$

240nm

Single-electron transistor (SET)

• Higher temperature operation

Single-electron memory

The Coulomb diamond characteristics of Si-SET (4.2K) Coulomb oscillation and PVCR comparison at RT Dot 1 Dot 11 v current (pA) Drain ( 30 40 50 Gate voltage (V) Dot 22 Dot 60 dot 1 Maxir num PVCR : 3.5 Larger PVCR is expected for multiple dots se total capacitance of multiple dots is smaller than that of a single dot. beca Single dot ( $C_{single} = C_g + 2C_j$ ) > Multiple dots (dot:  $\infty$ ,  $C_{multi} = \sqrt{C_g^2 + 4C_jC_g}$ (Cg: Gate capacitance, Ci: Junction capacitance) PVCR is calculated on the basis of orthodox theory by considering only - V \_: I = 1pA over 0.12 In Coulomb blockade region the single tunneling process the threshold voltage  $V_{\rm th}$  increases with the number of the multi junction array  $PVCR = \sinh \left| \frac{e}{2C_{total}K_{B}T} \right| / \frac{1}{2C_{total}K_{B}T}$ 1.5 C<sub>total</sub>[aF] 0.0 Σ PVCR vs total capacitance As the number of dot increases (Co-tunneling process is negligible at RT) the Coulomb blockade regions are bigger 0.0 Large PVCR is advantageous to circuit operations Multi tunnel junction works effectively XOR circuit operation at RT 20 30 40 50 Inhibiting the co-tunneling Determination of the input gate voltage Drain current switching characteristics junction numb and thermal activation Vat vs Tunnel junction number (4.2K) Nearly equal  $I_d$  oscillation for  $V_{g1}$  and  $V_{g2}$ Input 1.2 15V 1.2 0.8 0.0 0.6 Application of SET to XOR voltage 19.3V (Gate capacitance :  $C_{g1} \approx C_{g2}$ ) 15V Л Input 1 Vg Truth table for XOR (Ad Easy application of SET to XOR Sum of the XOR outpu Input 1 Input 2 Drain 0.6 current gate tage T=300K LH HL 0(L) 0(L) 0 (LL) 0(L) 0.4 -V<sub>d</sub>=1m\ Input voltages Output current 0(L) 1(H) 1 (LH,HL) 1 (H) Drain o 0. ĤH LL=30V

Gate voltage (V)

L oscillation of SET with 22dots

at RT as a function of Vg1 or Vg2

sweep V<sub>g2</sub>=0V, V<sub>g1</sub>=0V V

### Conclusion

(V.,

- We fabricated a highly doped Si-SET with multiple dots and double gates.

- A PVCR up to 77 was observed at RT for the SET with 22 dots

- We observed larger PVCR for some SETs with multiple dots than that for SET with a single dot.

LH,HL=34.3V -

ιL

Input voltage of L=15V and H=19.3V

HH=38.6V

We applied the Coulomb oscillation and the multiple gate input characteristics to an XOR operation and achieved a successful Id switching at RT

T

Н

time (s)

Id-time characteristics

Successful XOR operation at room

temperature