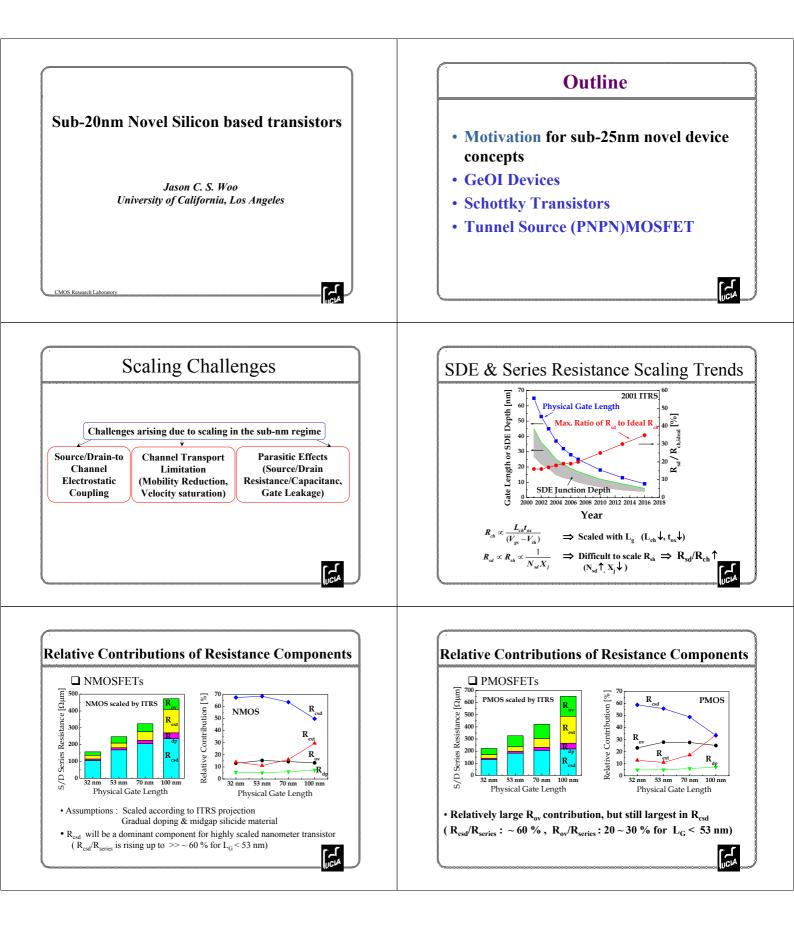

# Sub-20nm Novel Silicon based transistors

Yu-Lin Chao, Venkaragirish N., Ritesh Jhaveri, Ahmet Tura, and Jason C. S. Woo Department of Electrical Engineering, University of California, Los Angeles

Aggressive MOSFET scaling faces the challenges of limited Ion/Ioff ratio and severe short channel effects. To overcome these problems, new device configurations made feasible by small dimensions and new materials need to be explored. In this paper, novel devices incorporating silicon and germanium are presented. These silicon and germanium based asymmetric source injection devices with superior performance have the potential to alleviate the scaling challenges for sub-25nm nodes.

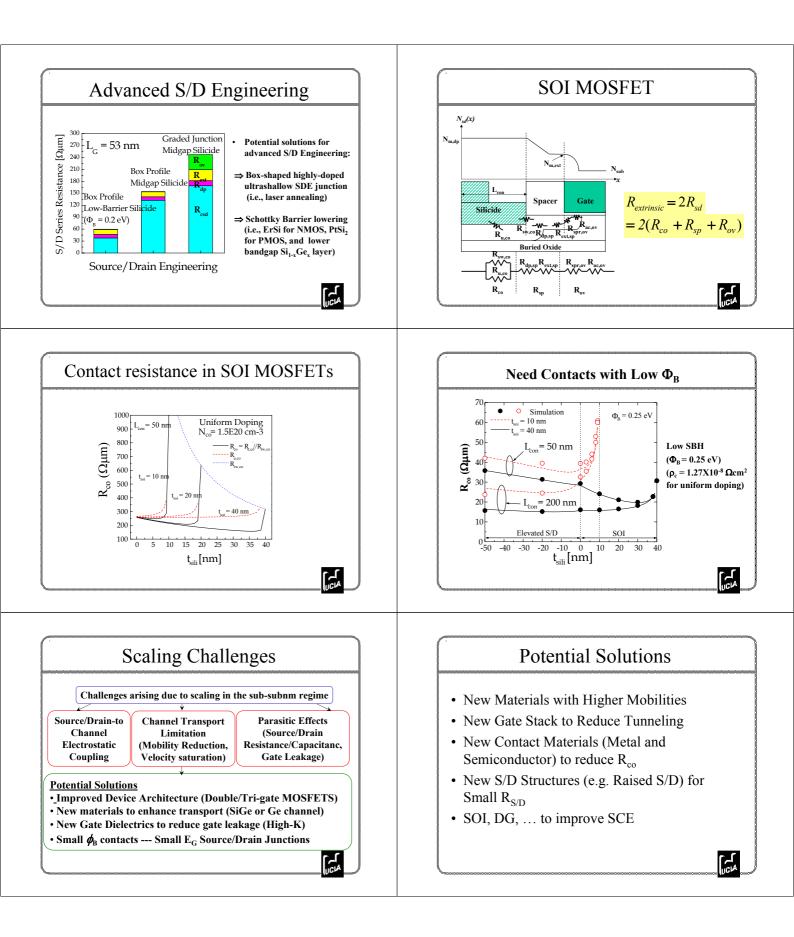

#### 1. Schottky Barrier MOSFET

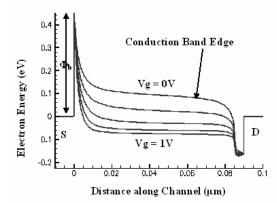

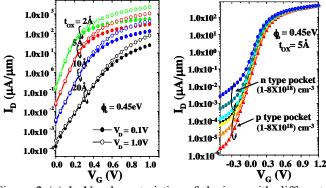

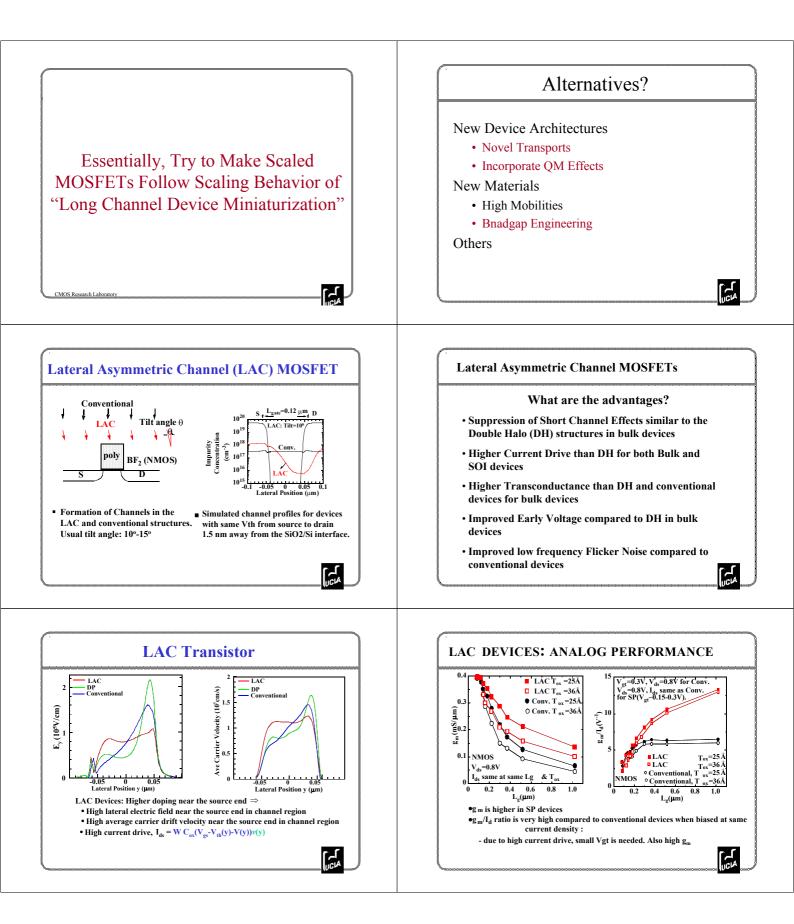

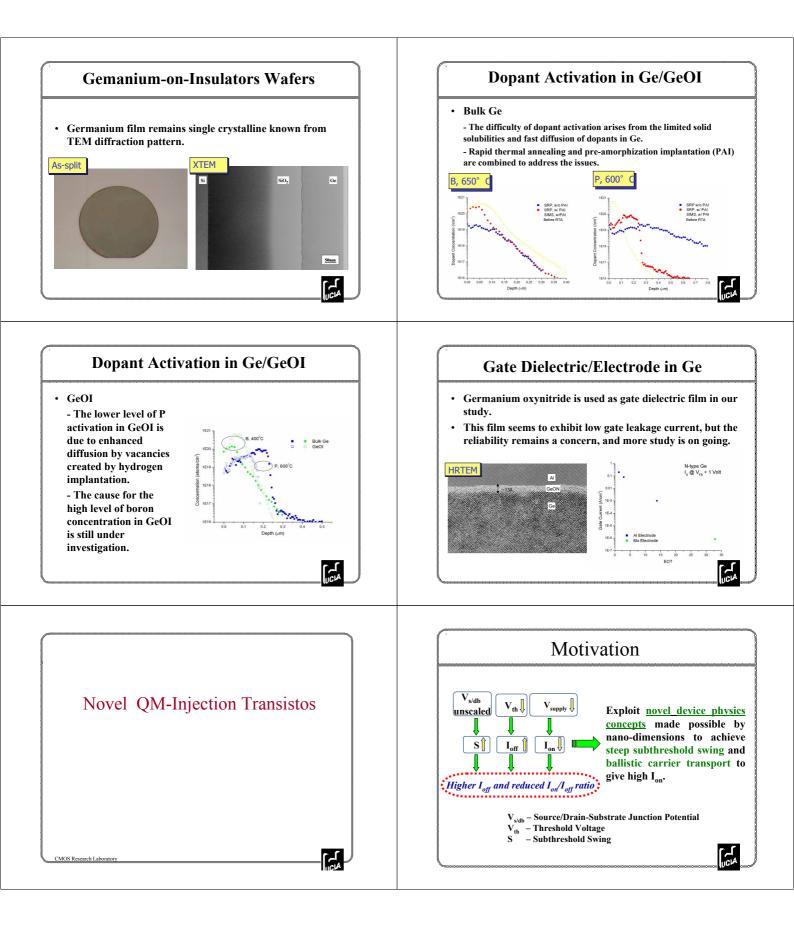

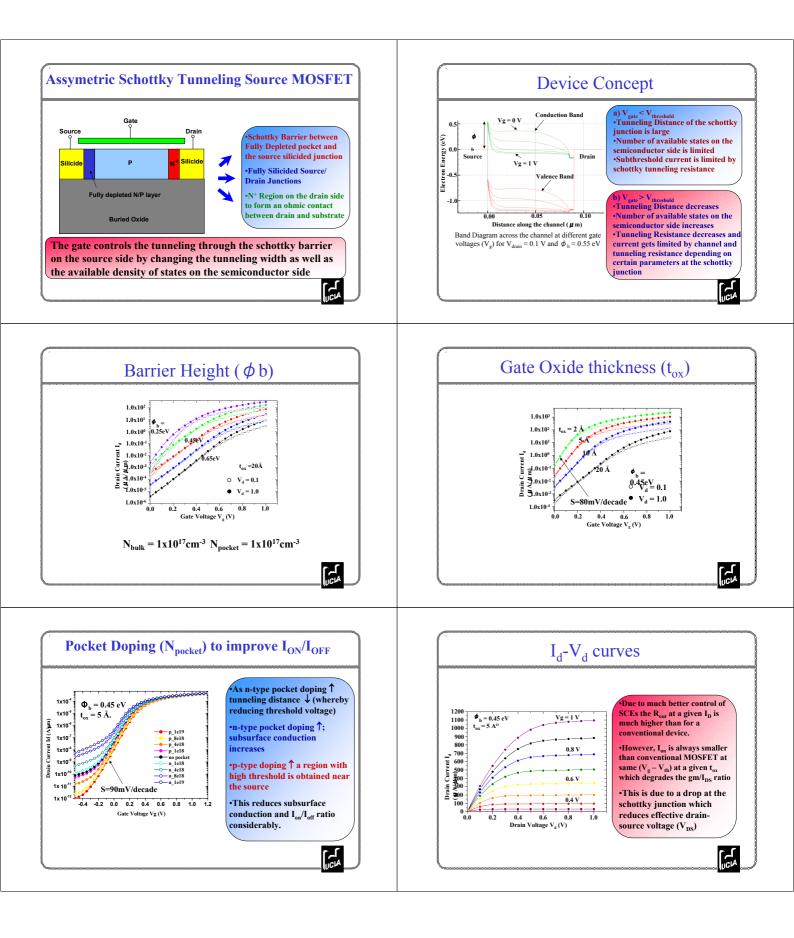

Schottky barrier MOSFETs which use fully silicided source/drain junctions have been proposed for future veryshort-channel devices 0. The major advantage is the formation of ultra shallow junctions with very low resistively. In this abstract, a novel asymmetric Schottky Tunneling Source MOSFET is introduced. The operating principle of the STS MOSFET utilizes the concept of gate controlled Schottky barrier tunneling between a metal and a semiconductor. Fig. 1 shows the band diagram along the surface of the channel region at different gate voltages for a Schottky source with a barrier height ( $\phi_b$ ) of 0.45eV. When the gate voltage is sufficiently low the tunneling distance of the Schottky junction is high as well as the number of states that electrons can tunnel into is small. Hence the current injection is limited by the tunneling resistance only. As the gate voltage increases, the tunneling distance reduces and the number of states the electrons in the metal source can tunnel into increases thereby reducing the tunneling resistance. Fig 2a shows that as gate oxide thickness reduces, there is a marked improvement in STS MOSFET subthreshold characteristics as well as I<sub>ON</sub>. A sub-threshold swing of  $\sim 130 \text{mV/dec}$  is obtained for EOT = 20Å and  $\sim 70 \text{mV/dec}$  is obtained for EOT = 5Å. This suggests that the sub-threshold swing is a strong function of toox as opposed to diffusion barrier transport. However, the sub-threshold swing obtained due to gate controlled tunneling is always degraded as compared to possible diffusion limited sub-threshold best swing (~60mV/dec at room temperature); even though STS has excellent DIBL and V<sub>TH</sub> roll-off characteristics. To further improve the performance of STS transistor, Schottky FETs with asymmetric source/drain pocket is proposed. Fig 2b shows that as the source pocket is made n-type with increasing dopant density, the tunneling distance (and therefore tunneling resistance) reduces for a given gate voltage and the threshold voltage also reduces. But, the sub-surface conduction goes up thereby increasing the off current. However, when the pocket is made p-type, a region of high threshold is created near the source. This reduces the subsurface conduction considerably resulting in low I<sub>OFF</sub>. I<sub>ON</sub> on the other hand is not degraded

since the band-bending increases due to the p-pocket. Therefore, the tunneling width remains about the same as conventional STS transistor. The  $n^+$  pocket on the drain side forms a low resistance contact between the channel and the drain, eliminating the potential drop at the drain side due to the presence of a Schottky barrier.

Figure 1 Conduction Band Edge profile along the channel for different gate voltages.  $\varphi_b=0.45$ eV.

Figure 2 (a)  $I_D$ - $V_G$  characteristics of devices with different gate oxide thicknesses for a given  $\phi_b$  of 0.45eV.  $N_{BULK} = 1X10^{17}$  cm<sup>-3</sup>. (b)  $I_D$ - $V_G$  characteristics with different pocket doping.  $N_{BULK} = 1X10^{17}$  cm<sup>-3</sup>,  $t_{SI} = 60$ nm and  $V_D = 0.1$ V.

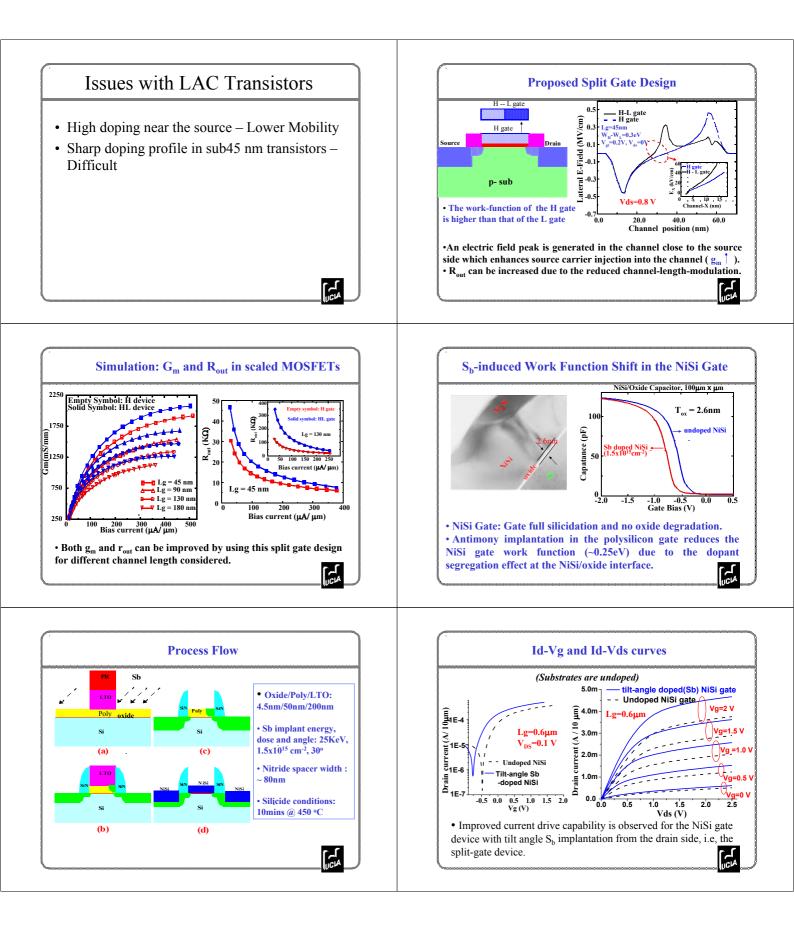

#### 2. Tunnel Source MOSFET

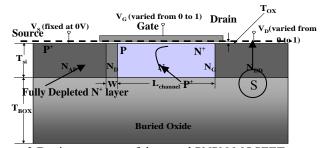

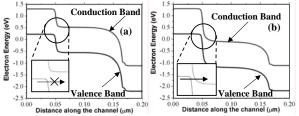

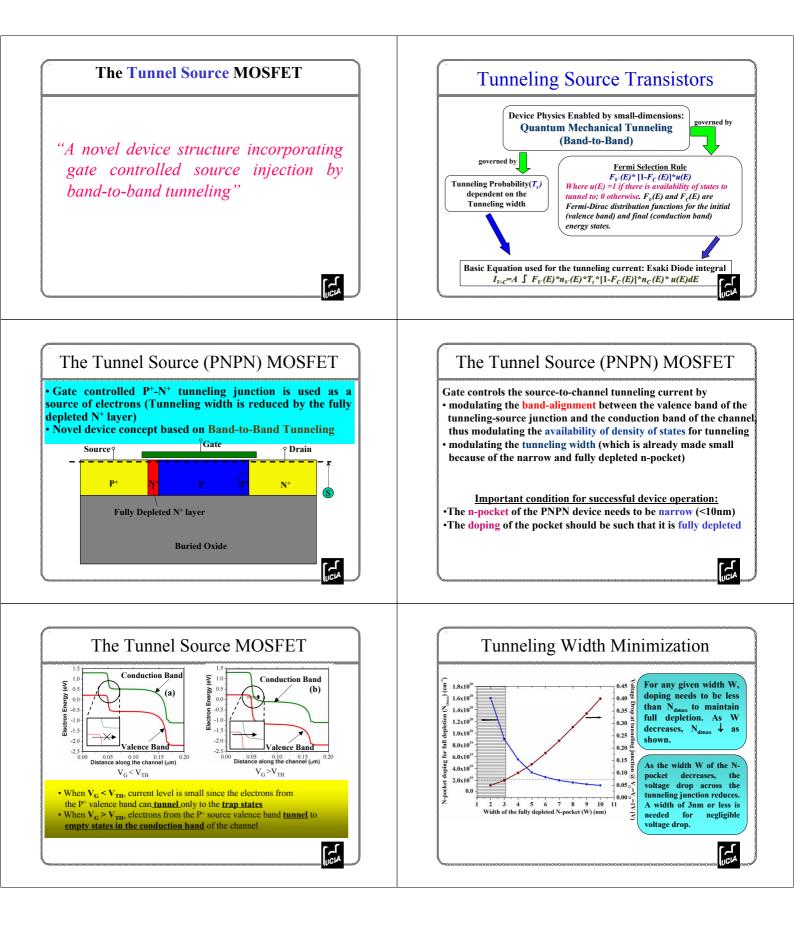

To further improve the  $I_{ON}/I_{OFF}$  ratio, we propose the Tunnel Source (P<sup>+</sup>N<sup>+</sup> tunnel diode) MOSFET [3]. The device structure of the novel asymmetric MOSFET is shown in Fig. 3. The gate electrode controls the source-to-channel tunneling current by modulating the band-alignment between the valence band of the P<sup>+</sup> tunneling source and the conduction band of the channel (thus modulating the availability of density of states for tunneling) and modulating the tunneling width (Fig 4).

Figure 3 Device structure of the novel PNPN MOSFET

Figure 4. Band Diagram along the channel along section S in Fig. 3. (a)  $V_G < V_{TH}$  (b)  $V_G > V_{TH}$ .

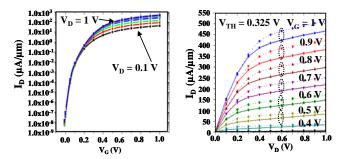

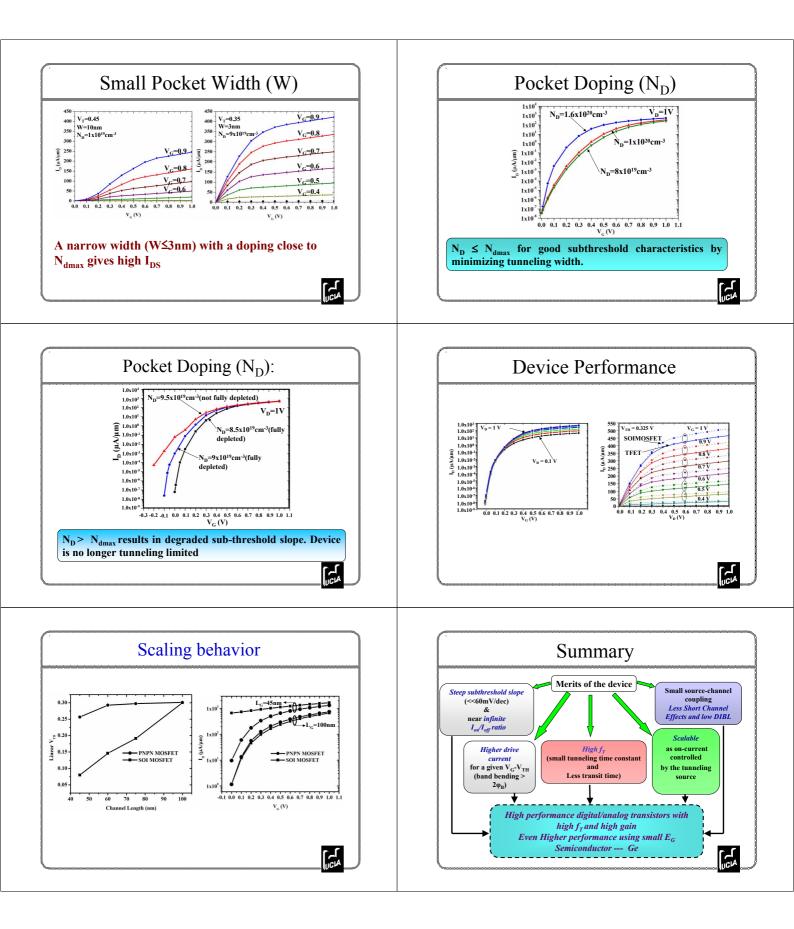

Detailed simulations show that the optimized novel PNPN MOSFET exhibits a steep sub-threshold slope (<<60mv/dec) (Fig 5a) with negligible DIBL. This is due to the fact that the overlap of the available density of states changes abruptly from zero to a finite value along with a reduction in tunneling width as the gate voltage increases from 0 to  $V_{\text{TH}}.$  Since the subthreshold behavior is determined by the tunneling source junction, DIBL is significantly reduced. Fig. 5b shows the I<sub>D</sub>-V<sub>D</sub> characteristics for the tunnel source MOSFET and a conventional SOI MOSFET. In the above threshold regime, the resistance of the tunneling junction is negligible for the PNPN MOSFET resulting in a current characteristic similar to a conventional SOI transistor. The threshold voltage (V<sub>TH</sub>) is defined as the gate voltage at which the channel conduction band overlaps with the source valence band. Therefore, for the same V<sub>G</sub>-V<sub>TH</sub>, the drive current is larger (band bending > 2  $\varphi_b$ ) for the PNPN MOSFET.

Figure 5 (a) Subthreshold Characteristics of a Tunnel Source FET. (b)  $I_D$ - $V_D$  characteristics for different  $V_G$  for the Tunnel Source FET (dotted) and conventional MOSFET (solid)

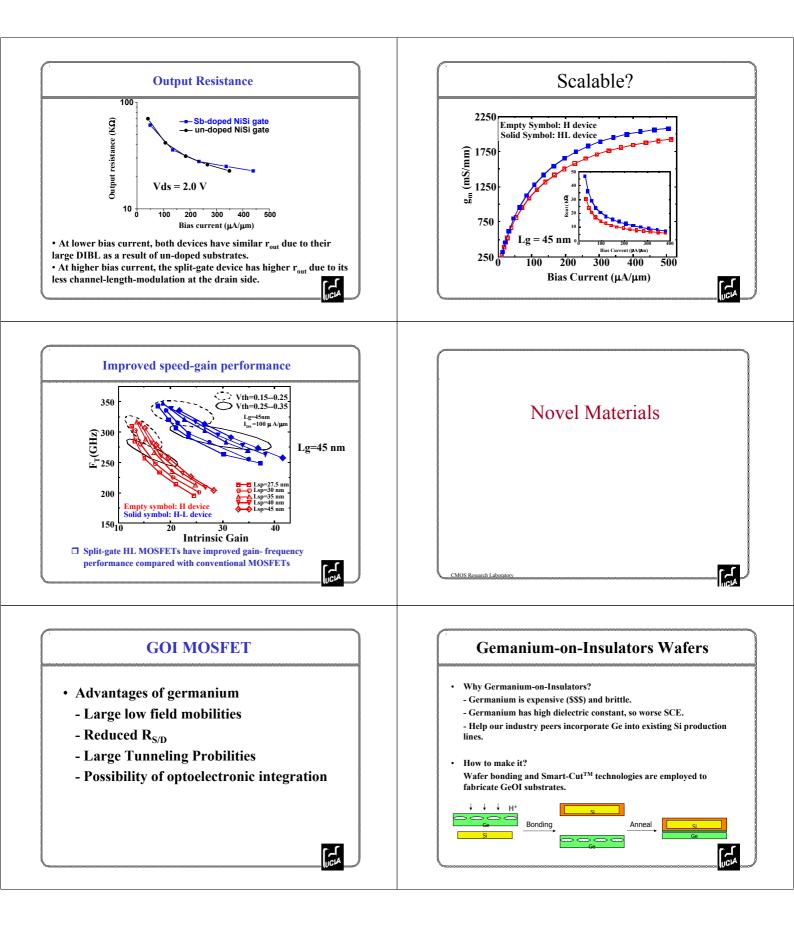

### 3. Tunneling transistors on GeOI

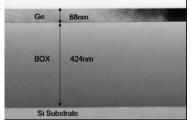

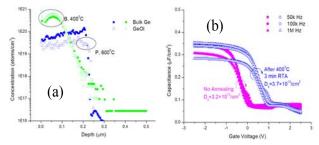

Germanium has regained attention for its low field high electron and hole mobilities which are beneficial for carrier transport in nanoscale devices. In addition, due to its smaller bandgap and therefore smaller tunneling width. Ge is the material of choice for both the Schottky FET and the Tunnel Source FET. To better control short channel effects and junction leakage current and to make germanium acceptable in current silicon production line, germanium-on-insulator (GeOI) is preferred. GeOI substrates can be obtained by wafer bonding and Smart-Cut<sup>TM</sup> techniques. A successfully transferred germanium on oxidized silicon wafer is shown in Fig. 6. The fabricated GeOI substrate has large amounts of vacancies which are the major diffusion vehicles in germanium. The electrical concentrations in bulk germanium and GeOI are then determined by the Fermi level dependency of dopants (Fig. 7a). Boron yields identical active concentration in two substrates, whereas phosphorous shows lower active level in GeOI due to faster diffusion assisted by charged vacancies, and this may affect scalability of germanium nMOSFETs. Another challenge of Ge devices is the quality of gate stack. A stable metal gate electrode against the selection of gate dielectrics is essential. In our study, Mo/germanium oxynitride gate stack is found to be thermally stable up to 400°C with interface charge density in the orders of  $10^{12}$  /cm<sup>2</sup>, as shown in Fig. 7b. A further reduction of the charge density is still needed.

Figure 6 XTEM of a GOI sample

Figure 7 (a) Electrical concentrations of n- and p-type dopants in bulk Ge and GeOI (b) C-V curves of Mo/germanium oxynitride gate stack before and after annealing.

## 4. References

[1] Moongyu Jang et al, IEEE Transactions on Nanotechnology, Vol.2, No. 4, pp 205-209, 2003.

[2] Kazuya Matsuzawa et al, IEEE Transactions on Electron Devices, Vol. 47, No. 1, pp 103-108, 2000.

[3] N. V. Girish, Ritesh Jhaveri and Jason C. S. Woo, IEEE 2004 Silicon Nanoelectronics Workshop, 2004, pp. 33-34.

# Conclusion

- New Device Structures Exploiting Physical Mechanisms Made Feasible by Nanodimensions

- Ge has Small  $E_G$  not just High mobilities

کہ

- Tunnel-Source Transistors Promosing

- Parasitics Still Need Special Attention