# Current status of PVD Hf-based high-k gate stack - Process improvement on drive current

M. Niwa<sup>1,2</sup>, R. Mitsuhashi<sup>1,2</sup>, K. Yamamoto<sup>1,2</sup>, S. Hayashi<sup>2</sup>, Y. Harada<sup>2</sup>, A. Rothchild<sup>3</sup>, T. Hoffmann<sup>3</sup>, S. Kubicek<sup>3</sup>, S. De Gendt<sup>3</sup>, M. Heyns<sup>3</sup>, and S. Biesemans<sup>3</sup>

<sup>1</sup> Matsushita assignee at IMEC 75 Kappeldreef, B-3001, Leuven, Belgium <sup>2</sup> Semiconductor Company, Matsushita Electric Ind.,Co., Ltd. Minami-ku, Kyoto, 601-8413, Japan <sup>3</sup> IMEC vzw, 75 Kappeldreef, B-3001, Leuven, Belgium

### Abstract

The electrical characteristics of high-k transistors using HfO<sub>2</sub> and its silicate gate dielectrics are investigated. These dielectrics are formed by an oxidation of co-sputtered Hf (and Si), followed by nitridation in NH<sub>3</sub> gas. In case of HfSiON gate dielectrics, due to its thermal robustness, lower gate leakage with good uniformity was achieved even after higher thermal treatment. Capacitance reduction due to its lower permittivity compared to HfO<sub>2</sub> is compensated by introducing of Ni-FUSI electrode to reveal high on-state drive current.[1] More highlighted is the effects of SiN capping between Ni-FUSI gate and PVD-high-k dielectric, and post deposition annealing(PDA) to suppress the reaction during FUSI process. The SiN cap was found to increase the yield of transistors, however, it could not suppress the instability of drive current characteristic. The reason for this is considered to be due to an interfacial reaction between high-k and electrode during the NiSi formation.[2] Also, it is noteworthy to arouse that the replacement of poly Si with FUSI gate causes not only the elimination of polydepletion but also the reduction of EOT.[3] Hereof, by optimizing the PDA condition, as an example, stable decent electrical characteristics were obtained for the Ni-FUSI/SiN/HfO<sub>2</sub> stack, i.e.,  $I_{on}(n/p) = 600/180 \text{ uA/um at } I_{off} = 20$  $pA/um at V_{dd}=1.1V$ . This excellent drivability meets low standby power specification of the MOSFET for 45nm node.

#### Introduction

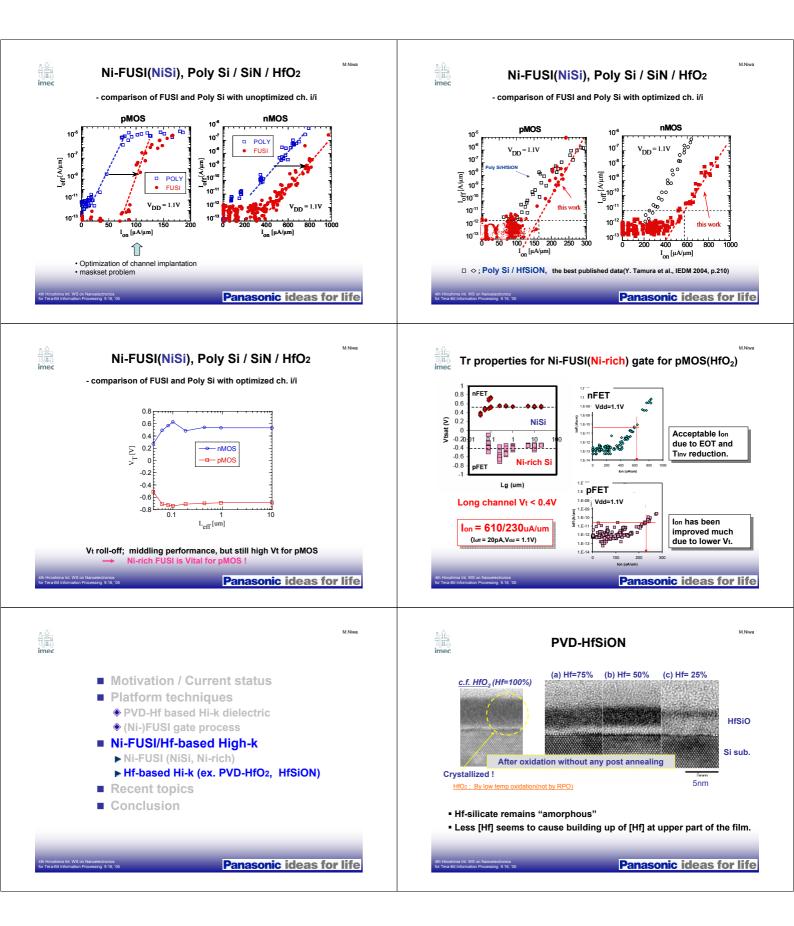

For LSTP application, it has been a serious challenge to compromise higher  $I_{on}$  with lower  $I_{off}$  with a suitable  $V_t$  value for high-k gate stacks.[4-7] Owing to its high  $C_{inv}$  and low EOT, Hf based gate stack with Ni-FUSI has become one of the promising candidate for LSTP application. Ni-FUSI is intensively investigated recently.[8,9] However, it is reported that FUSI/high-k gate stacks have worse uniformity and lower yield of transistors.[10] A systematic approach based on PVD has been employed in this work to enable optimized bi-layered gate stack by engineering the interface. In this talk, we investigate a formation of Hf-based high-k gate dielectric

formed by PVD method and demonstrate that the instability of FUSI/high-k system is caused by interfacial reaction between NiSi gate electrode and the high-k gate dielectric.

#### **Results and Discussion**

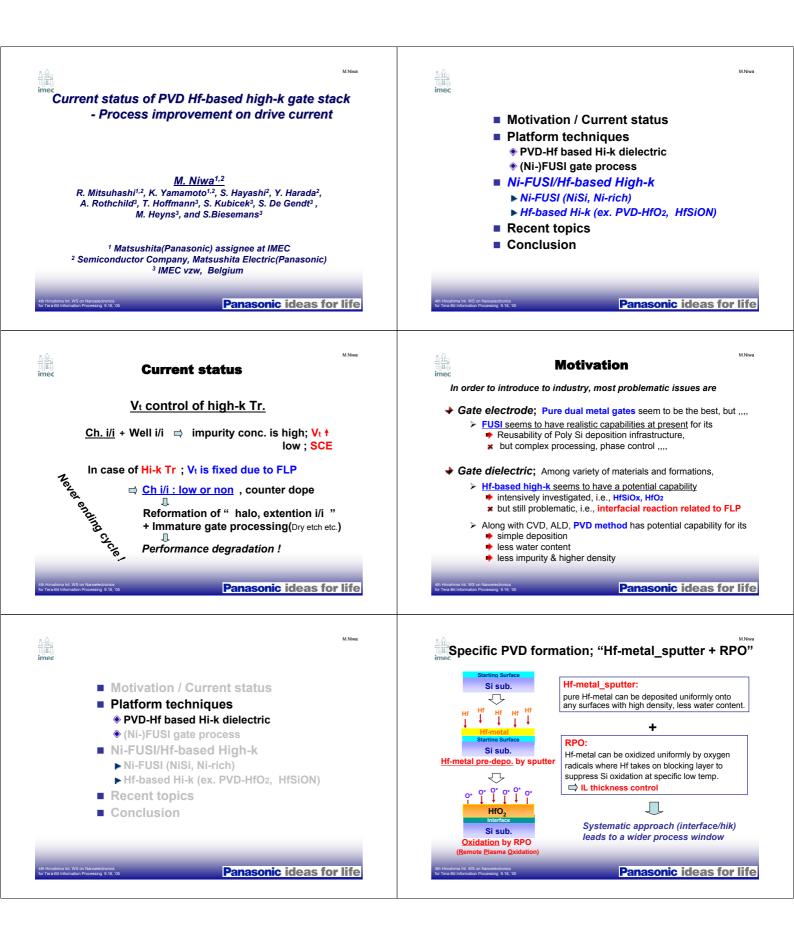

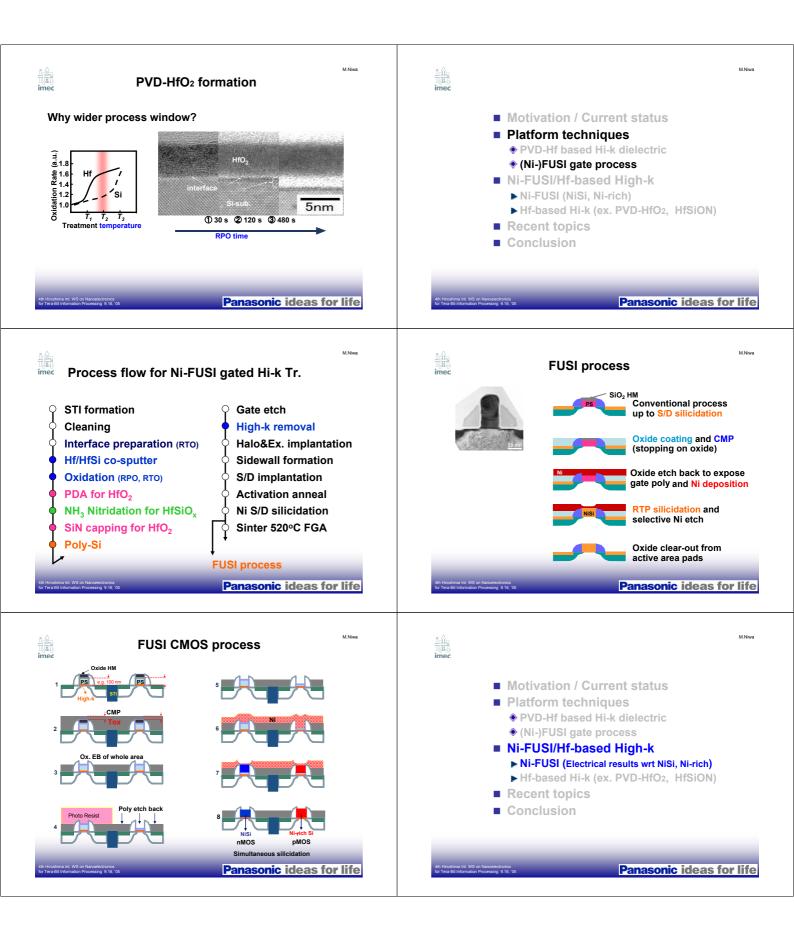

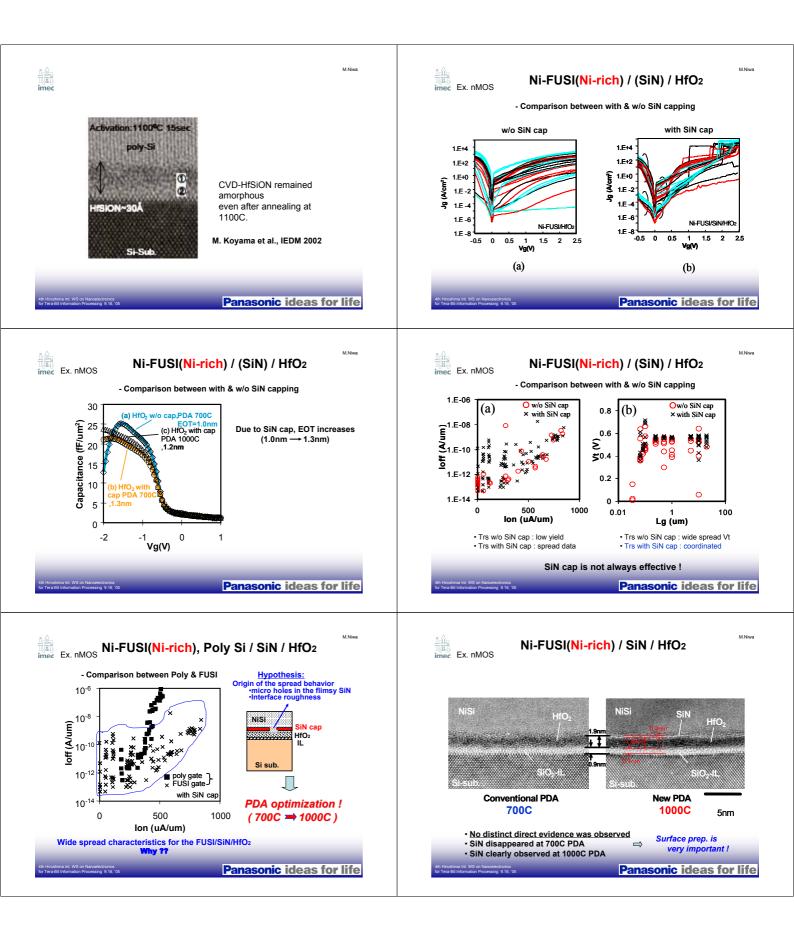

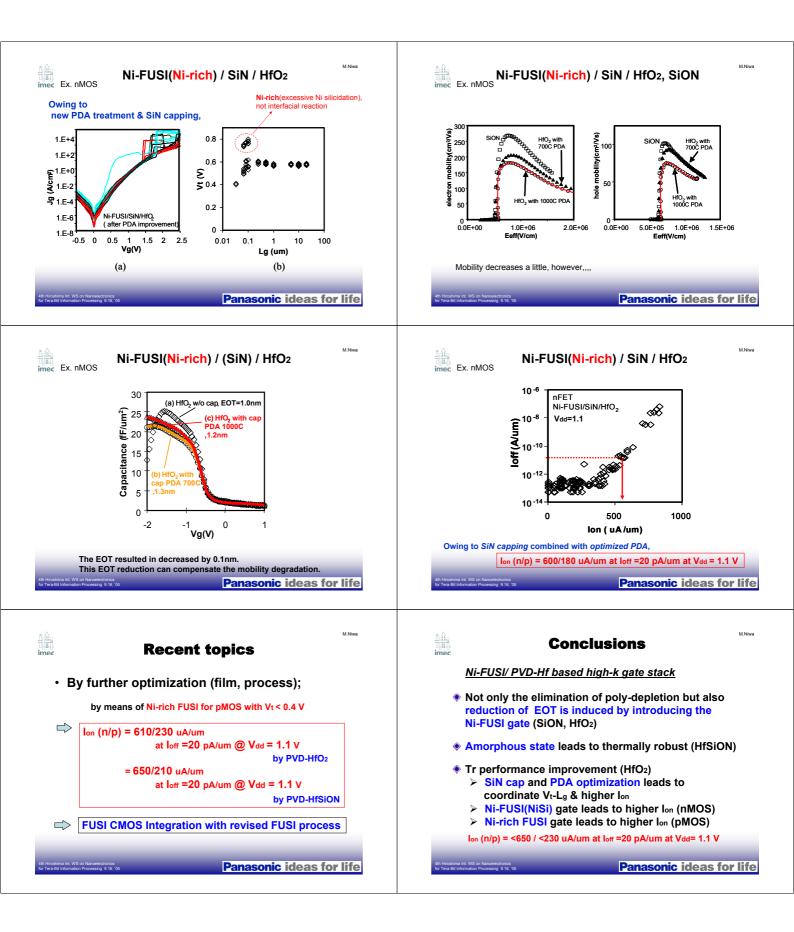

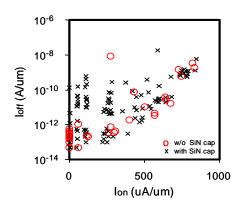

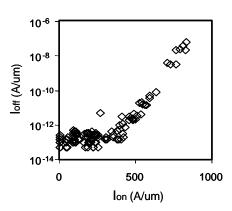

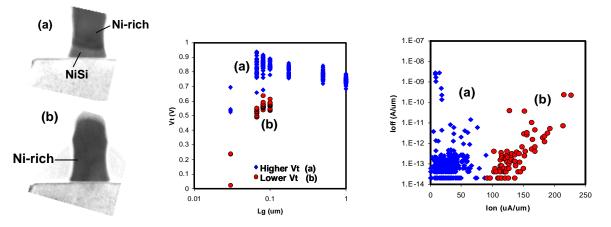

Poly Si, Ni-FUSI gated MOS FETs down to  $L_g = 50$ nm with (SiN)/HfO<sub>2</sub>,HfSiON/SiO<sub>2</sub> were fabricated by a conventional self-aligned process. The SiN capping on HfO<sub>2</sub> can act as a protective layer leading higher transistor yield, however, as shown in Fig.1, it cannot suppress a scatter in the I<sub>on</sub>-I<sub>off</sub> characteristics. Compared with Poly Si gated FETs, this trend is remarkable for the FUSI/SiN/HfO<sub>2</sub>/SiO<sub>2</sub>-FETs. However, this problematic scattering has been found to be drastically reduced when an elevated PDA temperature treatment is mainly introduced(Fig.2). This implies reaction-related phenomena, i.e., roughness or defects at upper interface between Ni-FUSI and HfO<sub>2</sub> are main causes of the electrical degradation. This is also confirmed by other experiments including V<sub>t</sub>-L<sub>g</sub>, J<sub>g</sub>-V<sub>g</sub>. In this respect, control of the upper interfacial reaction is a key issue for FUSI/high-k stacks.

By these treatments, excellent performance was obtained for the Ni-FUSI/SiN/HfO<sub>2</sub>/SiO<sub>2</sub>/Si system, i.e.,  $I_{on}$  (n/p) = 600/180 uA/um with  $I_{off}$  =20 pA/um at  $V_{dd}$ =1.1V.

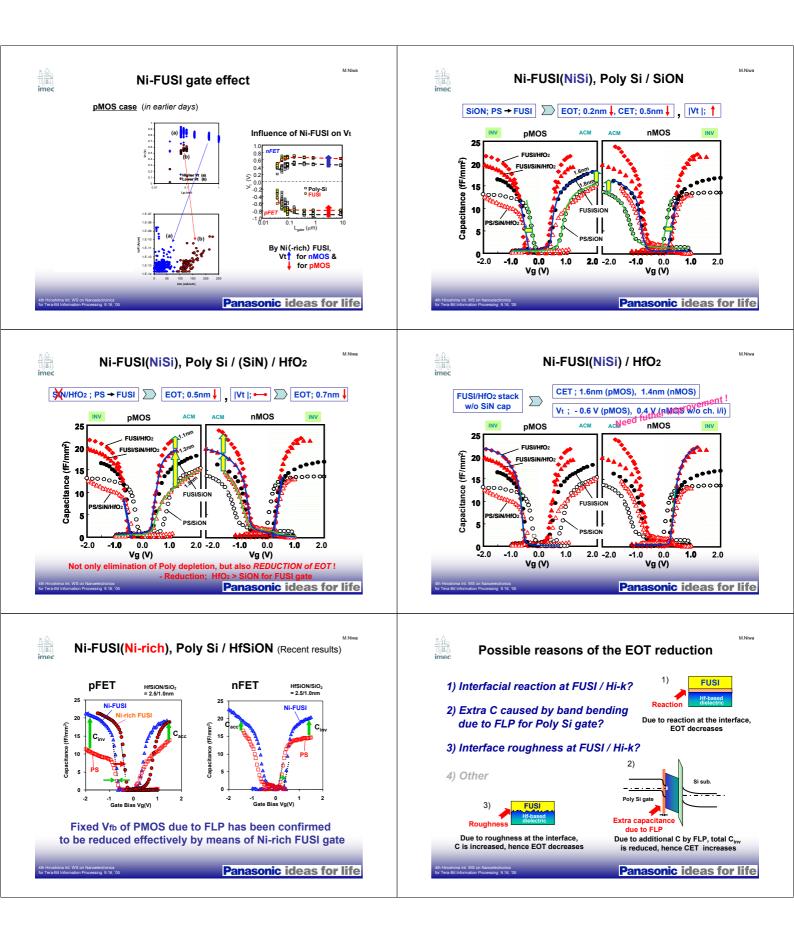

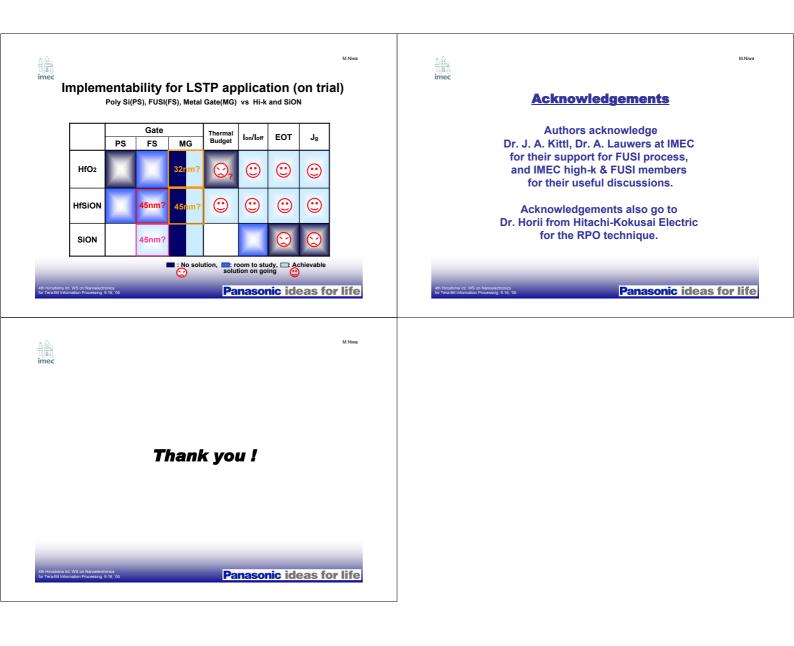

Meanwhile, different from the HfO<sub>2</sub>, NH<sub>3</sub> treatment plays a role of the SiN capping for Hf-silicate, since Si-N bonds rather than Hf-N can easily be formed in the HfSiOx. In case of the FUSI/HfSiON stacks with optimized NH<sub>3</sub> annealing, the scatter in the electrical characteristics was confirmed to be improved. This means the nitrided surface on the  $HfSiO_x$  is capable of protecting from the interfacial reaction. In addition, different from HfO2, Hf-silicate stays amorphous with less reaction with in the gate even after high temperature Si annealing(>1000C).[4] In spite of its lower k value than HfO<sub>2</sub>, the use of HfSiON with Ni-FUSI gate is worthwhile due to its EOT scalability and less gate leakage. Concerning FUSI potentiality, from process controllability point of view, variety of silicide phases can be produced in the gate due to narrowing effect of the gate.[8] Darker contrast in the XTEM image in Fig. 3 indicates a Ni-rich regime, conversely brighter contrast for a less Ni regime. Since each phase has respective work function, the phase control is primary important. Due to the work function difference, as shown for the pMOS case in Fig.3, Ni-rich gate can provide lower V<sub>t</sub>, hence high drivability, while NiSi gate provides higher V<sub>t</sub> with poor drivability as indicated by (b) and (a) respectively. We recently confirmed this occasional phase separation could be controllable. This presents a rosy picture. CMOS integration with wide process window is needed in addition to further material research towards potential bandedge (FUSI) gate.

## Conclusion

As far as performances are concerned, by suppressing the interfacial reaction between high-k and gate electrode and controlling the phase in the Ni silicide gate, Ni-FUSI/ HfSiON gate stack can be promising candidate for LSTP MOSFETs. There are pressing needs for its CMOS integration and reliability confirmation.

## Acknowledgements

Authors would like to thank Dr. A. Lauwers and Dr. J. A. Kittle at IMEC for their FUSI technology.

## References

- [1] K. Yamamoto et al., Proc. of INFOS, p198 (2005).

- [2] R. Mitsuhashi et al., Proc. of INFOS, p7 (2005).

- [3] M.Niwa et al., NATO Advanced Research Workshop on "Defects in Advanced High-k Dielectrics", St. Petersburg, 2005 to be published.

- [4] M. Koyama et al., IEDM Tech. Digest, San Francisco, 2002, p.849.

[5] J. Kedzierski et al., IEDM Tech. Digest, Washington DC, 2003, p.315.

- [6] Y. Tamura et al., Symp. on VLSI Technology, Honolulu, 2004, p.210.

- [7] E. P. Gusevet al., IEDM Tech. Digest, San Francisco, 2004, p.79.

- [8] J. A. Kittle et al., Symp. on VLSI Technology, Kyoto, 2005, p.72.

- [9] S. Kubicek et al., Symp. on VLSI-TSA, Hsinchu, 2005, p.99.

- [10] C. S. Park et al., IEDM Tech. Digest, San Francisco, 2004, p299.

**Fig. 1** SiN capping effect on I<sub>on</sub>-I<sub>off</sub> characteristics for FUSI/HfO<sub>2</sub> (nMOS)

Fig. 2 I<sub>on</sub>-I<sub>off</sub> of FUSI/SiN/HfO<sub>2</sub> after optimized PDA (nMOS).

Fig. 3 XTEM of Ni-FUSI/SiN/HfO<sub>2</sub> for pMOS. (a) indicates less Ni(Ni-rich) phase at lower(upper) part of the FUSI gate, and Ni-rich phase in the gate for (b). Darker contrast corresponds to Ni-rich regime.  $L_g$  dependence on  $V_t$  and  $I_{on}$ - $I_{off}$  characteristics with respect to (a) and (b) are also shown.