# A 1V Supply Low Noise CMOS Amplifier Using Noise Reduction Technique of Autozeroing and Chopper Stabilization

Yoshihiro Masui, Takeshi Yoshida, Takayuki Mashimo, Mamoru Sasaki and Atsushi Iwata Graduate School of Advanced Sciences of Matter, Hiroshima University E-mail: masui@dsl.hiroshima-u.ac.jp

## Abstract

A low-noise CMOS amplifier operating at a 1-V supply voltage is developed using the two noise reduction techniques of autozeroing and chopper stabilization. The proposed amplifier utilizes a feedback with virtual grounded input-switches and a multiple-output switched op-amp. The low-noise amplifier fabricated by a 0.18- $\mu$ m CMOS technology was measured at a 1-V power supply, and achieved low noise performance of 50-nV/ $\sqrt{Hz}$  input noise at 1-MHz chopping frequency.

#### Introduction

Recently, sensor chips using a mixed-signal CMOS technology have been applied for sensing and monitoring biological functions [1-2]. The low-noise amplifier is one of the most significant circuits in the sensor chip because of detecting small level signals. However the increasing of dc offset voltage (Voff) and flicker noise (Vfn) becomes a serious problem in scaled CMOS technologies.

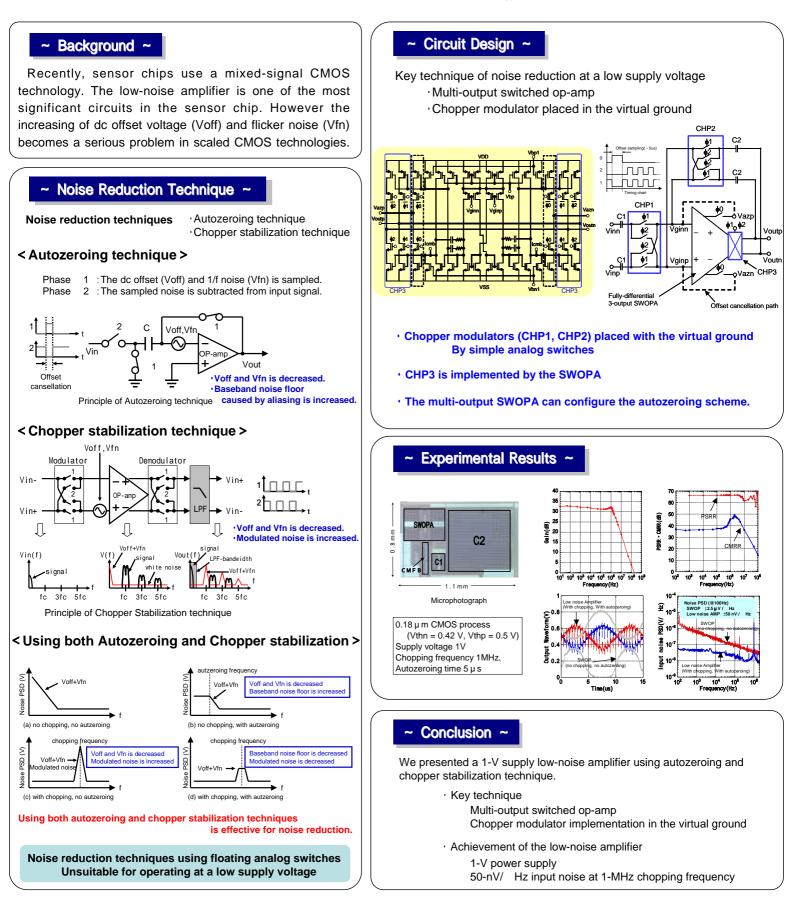

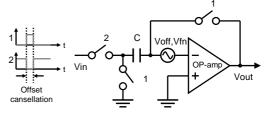

The autozeroing and chopper stabilization technique are used for reducing these noises [3]. The principle of these techniques is illustrated in Fig.1and2. The autozeroing technique samples the dc offset (Voff) and 1/f noise (Vfn), at phase  $\Phi 1$ . And then subtracts the sampled noise from input signal at phase  $\Phi 2$ . The autozeroing technique can reduce the low-frequency noise of amplifier. Although the autozeroing technique increases baseband noise floor caused by aliasing inherent in the sampling process (Fig.3(b)). The chopper stabilization technique converts the frequency range of input signal to a higher corner frequency, and then demodulates it back to the baseband after amplification. Although the large energy is presented at a chopping frequency (fc) due to the low-frequency noise (Fig .3(c)). The chopper stabilization technique equipped with the low pass filter (LPF) can provide the clean output signal. Using both autozeroing and chopper stabilization techniques enable a reduction of the baseband noise floor and the modulated noise at the chopper frequency (Fig .3(d)) [4].

However these noise reduction techniques using floating analog switches are not suitable for operating at a low supply voltage.

Fig. 1 Principle of Autozeroing technique

Fig. 3 PSD using noise reduction technique

#### **Circuit Design**

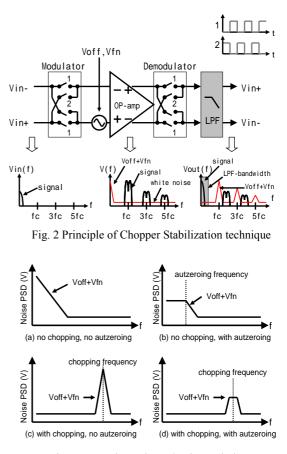

Figure 4 shows a equivalent circuit of the low-noise amplifier using autozeroing and chopper stabilization technique operating at a low supply voltage.

The chopper modulators (CHP1, CHP2) placed with the virtual ground are implemented by simple analog switches. Because a voltage level of virtual ground is possible to set to any level and input signal amplitude is small. On the other hand, the demodulator CHP3 placed outside the virtual ground is impossible to constitute analog switches because of large output amplitude. Therefore the CHP3 is implemented by the SWOPA. The CHP1, CHP2 and CHP3 are switched by the complementally clock signals of phase  $\Phi$ 1 and phase  $\Phi$ 2.

The multi-output SWOPA can configure the autozeroing scheme. During the phase  $\Phi 0$ , the output of SWOPA are connected to its input using dotted lines as shown in Fig. 4, so that it forms a voltage follower. The detected dc offset voltage is sampled into the hold capacitor C2; accordingly, the autozeroing operation cancels the dc offset. If the offset sampling is periodically, low-frequency noise also can be reduced.

autozeroing and chopper stabilization techniques

## **Experimental Results**

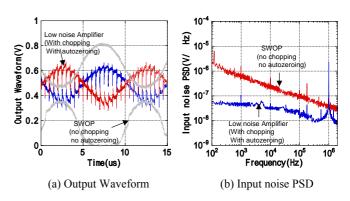

A test chip of the low-noise amplifier using chopper stabilization and autozeroing technique is fabricated with a 0.18-µm CMOS process (Vthn = 0.42 V, Vthp = 0.5 V). The measurements are shown in Fig. 5. The low-noise amplifier operated with 1-MHz chopping frequency and 5-µs autozeroing time at a supply voltage of 1 V. The input noise of SWOPA shows a typical 1/f noise spectrum, and the noise PSD is 2.5-µV/√Hz at 100 Hz. The proposed low-noise amplifier suppressed the noise PSD to less than 50 nV / √Hz.

Fig. 5 Measurements

#### Conclusion

In this paper, we presented a 1-V supply low-noise amplifier using autozeroing and chopper stabilization technique. The key technique of noise reduction at a low supply voltage is multi-output switched op-amp and chopper modulator implementation in the virtual ground. The low-noise amplifier fabricated with a 0.18- $\mu$ m CMOS technology was measured at a 1-V power supply, and achieved low noise performance of 50-nV/ $\sqrt{Hz}$  input noise at 1-MHz chopping frequency.

#### References

[1] T. Yoshida et al., "A design of neural signal sensing LSI with multiinput-channels", IEICE Transactions Fundamentals, vol. E87-A, No. 2, pp.376-383, Feb. 2004.

[2] C. C. ENZ et al., "Circuit Techniques for Reducing the Effects of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization", Proceedings of The IEEE, vol. 84, No. 11, pp.1584-1614, Nov. 1996.

[3] A. T. K. Tang, "A 3mV-Offset Operational Amplifier with 20nV/√Hz Input Noise PSD at DC Employing both Chopping and Autozeroing", ISSCC Digest of Technical Papers, pp.386-387, Feb.2002.

[4] V. Cheung et al., "A 1V CMOS Switched-Opamp Switched-Capacitor Pseudo-2-Path Filter", ISSCC Digest of Technical Papers, pp.154-155, Feb. 2000.

[5] Q. Huang, C. Menolfi, "A 200nV offset 6.5nV/√Hz Noise PSD

5.6kHz Chopper Instrumentation Amplifier in 1 m Digital CMOS", ISSCC Digest of Technical Papers, pp.362-363, Feb. 2001.

[6] J. F. Duque-Carrillo et al., "1-V Rail-to-Rail Operational Amplifiers in Standard CMOS Technology", Journal of Solid State Circuits, vol.35, No. 1, pp.33-44, Jan 2000.

[7] T. Yoshida et al., "A 1V Supply 50nV/√Hz Noise PSD CMOS Amplifier Using Noise Reduction Technique of Autozeroing and Chopper Stabilization", Symposium on VLSI Circuits Feb. 2005

# A 1V Supply Low Noise CMOS Amplifier Using Noise Reduction Technique of Autozeroing and Chopper Stabilization

Yoshihiro Masui, Takayuki Mashimo, Takeshi Yoshida, Mamoru Sasaki and Atsushi Iwata Graduate School of Advanced Sciences of Matter, Hiroshima University E-mail: <u>masui@dsl.hiroshima-u.ac.jp</u>