先端融合領域イノベーション創出拠点 「半導体・バイオ融合集積化技術の構築」 ナノデバイス・システム研究センター長 岩田

半導体技術とバイオ技術とを融合した領域の研究 は、有機材料と無機材料の接点、電子の世界のアナ ログ・デジタル情報と生命体の情報のインタフェー ス、新しい材料による超大規模メモリと多機能セン サーなど、学術、技術の進歩により将来の人間生活 に革新をもたらすものです。ナノデバイス・システ ム研究センターの21世紀COEプログラムの成果 を活用・発展させて、先端物質科学研究科の分子生 命機能科学専攻のグループと共同で研究課題「半導 体・バイオ融合集積化技術の構築」を提案しました。 2006年7月の採択が決まり、現在1年目の体制構 築を進めております。この拠点形成は大学と企業と の協働で行うもので、2006年度はエルピーダメ モリ株式会社と協働体制を構築しました。2007

年度はバイオ企業として生体分子計測研究所とも協 働体制を構築します。

この事業は文部科学省科学技術振興調整費および 協働企業の研究費により実施され、合わせて最低年 間6億円を投入し、最長10年の長期に渡る大型プロ ジェクトであり、10年後のイノベーションを創生す ることを目指しています。

融合領域の主要研究テーマとイノベーションは以 下の通りです。

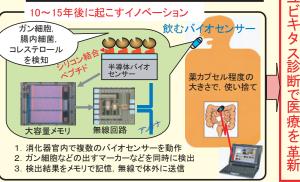

- (1) 新発見のシリコン結合ペプチドを用いてナノデ バイスに抗体などの有機分子を選択的に結合する シリコン・バイオ法を開発し、多項目・高速バイ オセンサを実現する。これを用いて医療を革新す るユビキタス診断システムを開発する。

- (2) 超大容量メモリのための新材料探索、新記憶原 理と記憶セル構造を考案し、次世代のテラビット メモリのプロトタイプを試作し、基盤技術を開発

- (3) ポストメモリとして、バイオセンサとメモリを

集積したブレインチップの基盤技術を 開発し、ユビキタス診断システムや ヒューマンインタフェース情報処理シ ステムの実現に資する。

現在、この融合領域の研究を立ち上 げるために、半導体・バイオ融合研究 の研究者、研究環境の構築を進めてい ます。また、先端物質科学研究科の修 士課程に「半導体・バイオ融合教育プ ログラム | をスタートさせます。この 融合領域研究に興味のある企業、研究 者、学生はご連絡ください。

(E-mail; iwa@dsl.hiroshima-u. ac. jp)

を

### 半導体・バイオ融合集積化技術の構築の概要

10年~15年後に起こすイノベーションの姿

高感度バイオセンサーと大容量メモリ、無線インターフェースを融合することで、 「飲むバイオセンサー」を実現し、ガンの早期診断や腸内細菌・コレステロール などの診断をいつでも、何処でも可能にする。

実施機関: 広島大学

協働機関: エルピーダメモリ(株),

半導体・ナノテク バイ オセンシング技術 (広島大学 ナノデバイス・システム研究センタ 先端物質科学研究科)

大容量メモリ技術 (エルピーダメモリ(株)

生体分子計測制御技術 (株)生体分子計測研究所) (株)生体分子計測研究所

## センター研究紹介

#### 超広帯域チップ間無線通信

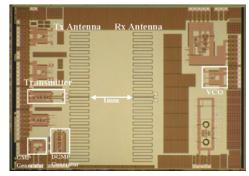

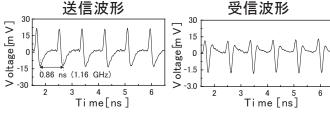

本研究では  $0.18~\mu m$  CMOS テクノロジーを用いて、パルス方式ウルトラワイドバンド通信のための、シングルチップガウシアン・モノサイクルパルス (GMP) 生成回路を開発しました。パルス幅 280~p s、リンギング・レベル -20.26~d B、中心周波数 3.6~G Hz の GMP 生成に成功しました。また、シリコン集積化ミアンダダイポールアンテナを用い、アンテナ間距離 1~m m において、送信レート 1.16~G bps の GMP 送受信に成功しました。この成果は 2006~e m Symposium on VLSI Circuits で報告いたしました。

#### 動画像認識のための並列処理 ハードウェアの設計

胸部断層イメージにおける 物体追跡の例

動画像の中の特定の物体を認識する方法には色々ありますが、「勾配ベクトルフロー(GVF)スネークモデル」という方法が、認識率が高く、どんな形状の物体の認識にも適用できる優れた方法であると言われています。しかし、数値計算の量が多いためこれまで実用的なものは実現されていませんでした。我々は、Field Programmable Gate Array を用いて、複数の数値演算ユニットによって並列処理をするシステムを設計しました。8-bit のカラー(256 色)QVGA サイズ画像(320×240 画素)において、20 フレーム毎秒の動画中の物体認識が可能です。胸部断層イメージにおける本方法による物体追跡の例を上に示しました。本成果は、2005 IEEE Int. Conf. on Advanced Video and Signal based Surveillance で発表されました。

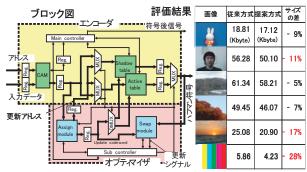

# リアルタイムに符号化テーブルの再構築を行う CAM を用いたハフマンエンコーダ

リアルタイムに符号化テーブルを最適化することが 可能な、Content Addressable Memory (CAM) を用いた 高速なハフマン符号化を実現するアーキテクチャを開 発しました。CAM は高速な一致検索機能を実行できる 機能メモリであり、この機能を利用することでハフマ ン符号化をリアルタイムに行えるようにするととも に、被符号化データの出現頻度にあわせて符号化テー ブルを再構築することで、圧縮率の向上も実現してい ます。デジタルカメラ等で利用されている JPEG 画像 圧縮に適用して検証を行った結果、圧縮率の大きいも のでは約28%の画像サイズの削減を実現することがで きました。また、符号化速度に関しても従来のアーキ テクチャと比較して平均95%ものクロックサイクル数 削減を実現しました。本研究の成果は論文誌、IEICE Trans. on Inf. & Systs., Vol. E90-D, No. 1, Jan, 2007 て発表されています。

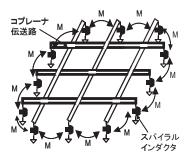

#### インダクタ負荷・結合の定在波発振器を 用いた高周波のクロック発生・分配

インダクタ負荷、インダクタ結合の定在波発振器を用いた高性能クロック発生・分配システムを考案しました。オンチップの伝送線路を用いた定在波発振器でメッシュ構成を作ると、位相のそろった  $10~{\rm GHz}$  以上の高周波クロックをチップ全面で得られるが、線路長が周波数によって制約されます。そこで、インダクタ負荷で、メッシュの距離と発振周波数を独立にする構成を考案しました。[1] さらに、伝送線路の終端インダクタを結合させて  $2~{\rm wr}$  次元メッシュを構成する方法を考案しました。 $0.~18~{\rm \mu m}$  CMOS 技術で  $12~{\rm GHz}$  動作のテストチップを設計・試作し、電源電圧  $0.9~{\rm V}$ 、消費電力  $80~{\rm mW}$  で、発振周波数  $11.~5~{\rm GHz}$ 、振幅  $0.~6~{\rm V}$  発振を得ました。ピーク・ピークジッタ  $4.~7~{\rm ps}$  の高性能を得ました。[2] [1] M. Sasaki et al., Dig. of Symp. on VLSI Circuits, pp.124-125, Iume 2006

[2] M. Sasaki et al., ISSCC Digest of Technical Papers, TP9.5, Feb., 2007.

## センター研究紹介

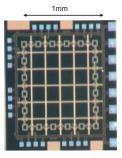

## 電気光学材料 (Ba, Sr) TiO<sub>3</sub> を用いた 光スイッチの Si 基板上 450℃低温形成

LSI の処理性能向上のために、長距離光配線を LSI に導入する研究を行っています。長距離配線は、複雑な短・中距離の金属配線の上層に作る必要があるため、金属配線の劣化しない 450  $^{\circ}$   $^{$

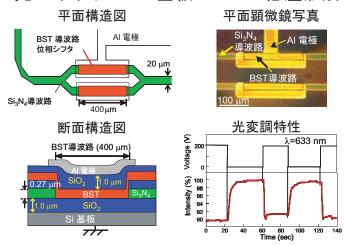

## 多重ドット Si 単電子トランジスタ における漏れ電流解析

単電子トランジスタ (SET) は超低消費電力を実現する次世代のデバイスとして期待されています。特に Si SET は現在までに蓄積した Si 集積化技術を利用できる利点を持っています。今回、多重ドットを有する Si SET を作製しクーロン振動の谷電流を測定してコトンネリング理論と比較し漏れ電流の起因を調べた結果、谷電流の温度依存性はドレイン電圧が低い場合、40 K以上では非弾性コトンネリング理論によってよく記述されることが示されました。この場合ドットを多重化することで谷電流が指数関数的に抑制できる事から、多重ドット構造は SET の高温高信頼性動作に有望である事が判りました。本研究の成果は、Applied Physics Letters, Vol.89, Art. No. 183520 において発表しました。

#### フルシリサイドゲート MOS デバイス

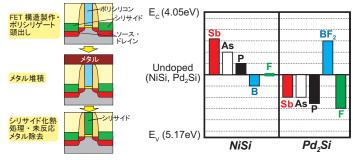

FUSI MOSFET の製造工程

FUSI MOS 構造の仕事関数 変調可能域

MOSFET のゲート電極には長年ポリシリコンが使われ て来ました。しかし、ゲート絶縁膜の薄層化に伴い、 これをメタルに置き換えることが検討されています。 メタルゲート形成には色々な手法がありますが、我々 は図のようにいったんポリシコンゲートを形成した後 にシリサイド化させる FUSI (Fully Silicided) ゲート を研究しています。FUSI ゲートでは、シリサイド化前 に不純物をポリシリコンに添加しておくことで仕事関 数変調が可能です。これは CMOS デバイスのしきい値 電圧の調節のために欠かせない特長です。FUSI ゲート の材料として最も一般的なのは NiSi ですが、我々は これよりも低温で形成可能で FET 製作工程への組み込 みが容易な、Pd<sub>2</sub>Siを用いた FUSI 構造の作成に成功し ました。Pd<sub>2</sub>Siの仕事関数変調域はNiSiと同等ですが、 仕事関数がシフトする方向が NiSi とは逆という興味 深い結果が得られており、仕事関数変調の機構解明に 役立つと考えています。

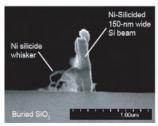

## 立体 Si ビームの NiSi 化技術

S i ビームから外部に張り 出したN i S i ウィスカー (未反応N i 除去後)

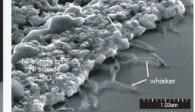

N i 粒界に沿って形成された N i S i ウィスカー (未反応N i 除去後)

次々世代以降の最有力SiトランジスタとしてSiの梁(ビーム)を用いた構造が提案されています。この構造を有効に利用する要の技術の一つは低抵抗ビーム形成です。

このため Si ビームに Ni を堆積し、熱処理によって Ni Si を形成したところ、左図に示すような Ni Si のウィスカーが見られました。これは隣接パターンとの間に電気的短絡を引き起こす有害な現象です。確認のため平面で再実験したところ右図に示すような、 Ni 膜の粒界に沿って Ni Si が形成されたことがわかりました。 斯界でも報告されていない新規な現象で ADMETA 学界で発表しました。

この現象はNi が過剰に存在する場合の特異な現象であり、堆積量、堆積条件、熱処理条件を最適化すれば発生しないことを実験で確かめました。

## 新任教員·研究員紹介

平成18年度に、1名の海外客員教授と2名の研究 員を迎えました。以下に自己紹介します。

海外客員教授 肖 夏 (Xiao Xia): 中華人民共和国天 津大学電気情報工学科から参りました。研究テーマは、 「ウルトラワイドバンド電磁波による乳癌検出の研究」 です。正常組織と腫瘍組織では、マイクロ波に対する 電気的性質が大きく異なることを利用します。電磁波 の反射強度像によって腫瘍を捉えることができます。 研究員 雨宮嘉照: LSI チップ内光インターコネク ション技術の研究・開発を行っています。チップ内配 線を金属配線から光配線や光スイッチング素子を用い た集積回路に代えることにより、高速度の信号伝達に よる LSI 性能の向上を目指した研究を行っています。 研究員 熊木武志:多並列検索処理を実現することで、 知能情報処理やネットワーク分野等での効果的な利用 が期待できるマルチポート連想メモリ、及びマルチメ ディアデータ処理を高速、低消費電力で実現すること が可能なモバイル機器向けの超並列プログラマブルプ ロセッサの開発・評価を行っております。またこれら のアーキテクチャを用いることによる、画像や暗号等 の様々な処理の実現を研究しております。

#### センター利用希望・共同研究希望の皆様へ

ナノデバイス・システム研究センターは、広島大学の学内共同利用教育研究施設として設置されており、学 内は先端物質科学研究科や工学研究科の研究室の多くの方に利用されています。また、他大学・企業とは共同 研究・受託研究を実施したり、研究員・社会人博士課程後期学生の受け入れを行っております。ご興味がござ いましたら、センター教員までご連絡ください。 TEL: 082-424-6265

e-mail: nanotech@hiroshima-u.ac.ip

また、文部科学省ナノテクノロジー総合支援プロジェクトの一環として、シリコンを主体とする超微細構造 形成のための支援(現在は無料ですが平成19年度より有料化を検討中)を行っており、ナノ構造形成プロセス、 超微細デバイスに関する技術相談(随時)にも応じています。学内、他大学、民間企業等からの支援申し込み を受け付けております。詳細は、ウェブページ http://home.hiroshima-u.ac.jp/nanotech/をご覧ください。

## ナノデバイス・システム研究センター研究組織

# ナノデバイス研究領域:

教授・吉川公麿(先端物質科学研究科兼担) 助教授・芝原健太郎(先端物質科学研究科兼担) 国内客員教授· 水野正之 (NEC(株))

#### ナノプロセス研究領域:

教授・横山新(先端物質科学研究科兼担) 助教授・中島安理 (先端物質科学研究科兼担)

#### システム設計・アーキテクチャ研究領域:

教授·Mattausch, Hans Juergen (先端物質科学研究科兼担) 助教授・小出哲士(先端物質科学研究科兼担)

海外客員教授・肖 夏 (Xiao Xia) (天津大学)

#### 分子集積機能研究領域:

教授・角南英夫 (先端物質科学研究科兼担)

学内共同研究員:関連学部・学科 17名

客員研究員(他大学、企業):6名

研究員: Ahmadi Ali、雨宮嘉照、池田弥央、大倉健作、奥山清、 茅場靖剛、佐々木信雄、田主裕一朗、田部井哲夫、長義紀、 細井卓治、Zhu Shiyang

学生:50名(ナノデバイス・システム研究センター)、52名(工学部、 工学研究科、先端物質科学研究科、理学部、総合科学部)

事務補佐員、研究支援推進員:葦原千秋、市原妃奈、(金野節子) 國貞尚子、久保田明子、(久良佳都子)、門前智美、淀川恭子

電話: 082-424-6265

センター長

顧問

産総研

半導体先端

ルネサス

テクノロジーズ

e-mail: rcns@sxsys.hiroshima-u.ac.jp

教授・岩田 穆 (併任)

URL: http://www.rcis.hiroshima-u.ac.jp/rcns/

運営委員会

廣瀬 全孝

渡辺 久恒

西村 正

FAX: 082-424-3499