# 広島大学ナノデバイス・システム研究センター

# Research Center for Nanodevices and Systems Hiroshima University

# 設立の目的と経緯

# Aim and Background of Foundation

ナノデバイス・システム研究センターは、最先端半導体集積回路技術と新しいコンピュータシステムの基礎研究を推進する学内共同利用教育研究施設である。本センターは1986年に設立された集積化システム研究センターの10年時限到来を受けて、1996年5月に新たに設立された。新センターでは、集積化デバイス・プロセス・材料・システムの研究を融合的に推進する。具体的な研究の目標は、(1)テラ(1兆)スケールの集積度をもつULSI実現に必要な数十ナノメータ(1ナノメータは10億分の1m)サイズの極微細トランジスタの開発と素子物理の解明、(2)極微細トランジスタの性能向上の為の新しいデバイス構造、革新的な加工プロセス及び材料の研究、(3)光配線を含む高速配線技術の研究、(4)柔軟な知能情報処理を実現するためのコンピュータアーキテクチャの研究及びその要素技術としてのマルチポートメモリの開発、などである。

2002年にナノデバイス・システム研究センターは、21世紀COEプログラムによる研究拠点「テラビット情報ナノエレクトロニクス」に選定されました。これまでにセンターで達成した半導体分野の世界レベルの研究成果と人材・技術・設備などのリソースを活用して、情報エレクトロニクスに関する世界で認められた研究拠点を形成します。

The Research Center for Nanodevices and Systems (RCNS) is performing fundamental research for advanced integrated circuit technologies and a new computer system. RCNS was founded in May 1996 and is based on the research achievement at the Research Center for Integrated Systems, whose scheduled term was from 1986 to 1996. Research objectives at RCNS are (1) development of ultra-small-dimension transistors for tera-scale integration with a few tens of nanometers (1 nanometer=10-9m) gate length and a systematic study of the related device physics, (2) proposal of new transistor structures and development of the necessary innovative fabrication processes and materials technologies, (3) high-speed interconnect technology including optical interconnects, (4) study on new system architectures for flexible, intelligent information processing and the related component architectures such as high-performance multiport-memories.

The RCNS has been selected as the Center of Excellence (COE) on "Nanoelectronics for Terabit Information Processing" based on the 21<sup>st</sup> COE program, in 2002. The scientific staff of RCNS and the cooperating members of the Graduate School of Advanced Sciences of Matter intend to form a COE for innovative research and education on information electronics by extending their world-class research position.

January 2004

ナノデバイス・システム研究センター長

Director Research Center for Nanodevices and Systems Hiroshima University

岩田 穆

Atsushi Iwata

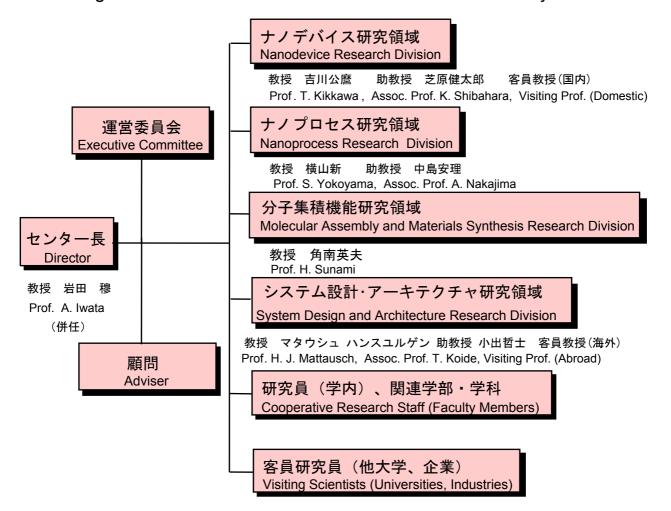

# ナノデバイス・システム研究センター組織

Organization of Research Center for Nanodevices and Systems

### 学内共同研究

Cooperation within Hiroshima University

#### 21世紀COEプログラム 21st Century COE Program

テラビット情報ナノエレクトロニクス

Nanoelectronics for Tera-bit Information Processing

#### 大学院先端物質科学研究科

Graduate School of Advanced Sciences of Matter

#### 大学院工学研究科

Graduate School of Engineering

#### 大学院理学研究科

Graduate School of Science

#### 放射光科学研究センター

Hiroshima Synchrotron Radiation Center

#### ベンチャービジネスラボラトリー

Venture Business Laboratory

### 社会との連携

Cooperation with Society

#### 産学共同研究

Cooperative Research with Industries

#### 地域共同研究

Regional Joint Research

#### 大学間共同研究

Interuniversity Cooperative Research

#### 国際共同研究

International Cooperative Research

#### ナノテクノロジー総合支援

Nanotechnology Support Program

# センターの研究領域

### Research Areas

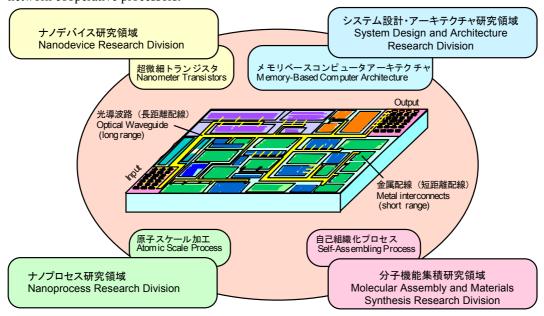

#### (1) ナノデバイス研究領域

超大容量メモリとプロセッサを同一基板上にテラ(一兆)スケールで集積化するための極限微細デバイスの開発及び次世代多層配線技術・ワイヤレス配線・光配線技術の研究

#### Nanodevice Research Division

Development of ultra small dimension transistors with a size of a few tens of nanometers and related nanodevices for a tera-scale integrated system consisting of memories and processors on a single chip, and research on advanced interconnect technology, wireless interconnect technology and optical interconnection.

#### (2) ナノプロセス研究領域

極限デバイスの超大容量集積化に必要な原子スケール加工技術開発及びナノ構造形成プロセスの診断技術の研究

#### Nanoprocess Research Division

Development of atomic-scale process technologies, and study of atomic-scale, *in situ* monitoring technologies for extremely large scale nanodevice integration.

#### (3) 分子集積機能研究領域

分子・基板表面固有の物理・化学的性質を利用して、自己組織的に集積ナノ構造を構築し、 それを超微細デバイス作製に応用する研究

#### Molecular Assembly and Materials Synthesis Research Division

Study of self-assembling processes utilizing specific physical or chemical nature of a source gas or a substrate surface, by which nanostructures are integrated to realize functional units such as memory and logic.

#### (4) システム設計・アーキテクチャ研究領域

超大容量メモリ内に分散配置されたプロセッサにより、メモリブロック間の相互作用を制御するメモリベースの柔軟な知能情報処理システムの設計法を研究

#### System Design and Architecture Research Division

Study of memory-based flexible and intelligent information-processing systems in which data processing is carried out by interaction among ultra large scale memory units and is controlled by network cooperative processors.

センターの研究領域 Research Divisions at RCNS

# 研究テーマ Research Themes

1. ナノデバイス技術 (Nanodevice Technology)

ナノメータ/ワイヤレス・インターコネクトの研究

(Nanometer-scale / Wireless Interconnects)

(Takamaro Kikkawa)

吉川公麿

ナノメータMOSFETの研究 芝原健太郎

(Nanometer-scale MOSFETs) (Kentaro Shibahara)

三次元立体MOSFETの研究 角南英夫

(3D-MOSFETs) (Hideo Sunami)

シリコン新機能デバイスの研究 中島安理

(Si New Functional Devices) (Anri Nakajima)

光配線LSIの研究 横山新

(Optically Interconnected LSI) (Shin Yokoyama)

2. ナノプロセス技術 (Nanoprocess Technology)

MOSトランジスタの微細化プロセスの研究 横山新

(Fabrication Processes of Nano-MOSFETs ) (Shin Yokoyama)

高誘電率ゲート絶縁膜の原子層成長法の研究 中島安理

(Atomic-Layer-Deposition of Ultrathin Gate Dielectrics ) (Anri Nakajima)

多層配線材料プロセスの研究 吉川公麿

(Interconnect and Low-k Materials and Processes) (Takamaro Kikkawa)

3. 分子集積機能技術 (Molecular Assembly and Materials Synthesis Technology)

自己組織化プロセスによるナノ構造形成法の研究 宮崎誠一\*、角南英夫 (Fabrication of Nanostructures by Self-Assembling Processes)

(Seiichi Miyazaki\*, Hideo Sunami)

\*大学院先端物質科学研究科(Graduate School of Advanced Sciences of Matter)

4. システム設計・アーキテクチャ技術 (System Design and Architecture)

多ポートメモリの研究 マタウシュ ハンス ユルゲン (Hana Jürgan Mettauseh)

(Multi-Port Memories) (Hans Jürgen Mattausch)

連想メモリの研究マタウシュ ハンス ユルゲン(Associative Memories)(Hans Jürgen Mattausch)

メモリベース学習の研究 小出哲士

(Memory-Based Learning) (Tetsushi Koide)

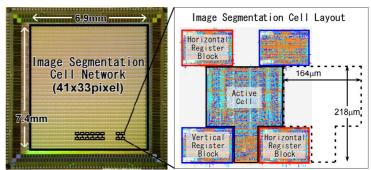

画像分割と特徴抽出の研究 小出哲士

(Picture Segmentation and Feature Extraction) (Tetsushi Koide)

# ナノデバイス研究領域

### Nanodevice Research Division

#### ナノメータMOSFETの研究 (Nano-Meter-Scale MOSFETs)

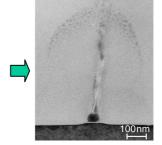

MOSFET 微細化に伴う技術的諸問題の解決のために、極薄ゲート酸化膜 MOSFET やゲート長 30nmMOSFET を開発した実績がある。現在では微細化による性能向上を極限まで追求するために、 ソース・ドレイン極浅接合形成法やメタルゲート仕事関数変調などの研究を行っている。

We are conducting research on technical problems due to MOSFET scaling. MOSFETs with ultra-thin gate oxides and 30-nm gate-length have been developed. In order to pursue the improvement of the performances, source and drain ultra-shallow junction formation and work function tuning of metal gates are conducted.

#### 極薄ゲート酸化膜 (Ultrathin Gate Oxide)

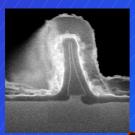

極薄1.2nmゲート酸化膜を有する MOSFETの断面TEM写真

Cross sectional TEM image of MOSFET with ultra-thin gate oxide (1.2 nm).

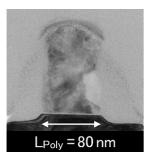

Sbを用いた極浅接合を有するゲート長30nm MOSFETの断面TEM写真

Cross sectional TEM image of MOSFET with ultra-shallow junction using Sb. Gate length is 30 nm.

#### 極浅接合 (Ultra-Shallow Junction)

斜め注入を用いてSb極浅接合とゲートの オーバーラップ長を稼ぎ電流駆動力を改 善したMOSFETの断面TEM写真

High current drivability MOSFET with Sb ultrashallow junctions, where overlap length between gate and the junctions is intentionally increased by tilted ion implantation.

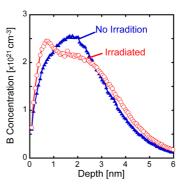

レーザアニールで形成したB極浅接合の深さ方 向ドーパントプロファイル。ナノ秒オーダの極 短時間熱処理ではBはほとんど拡散しない。

In-depth profile of B-doped ultra-shallow junction formed by the laser annealing. Ultra short duration annealing in the order of nano seconds leads to little diffusion of B.

#### メタルゲート (Metal Gate)

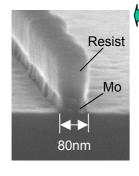

従来のポリシリコンに変えてMoを用いて形成した80nmのゲート電極断面SEM写真。

Cross sectional SEM photograph of 80 nm gate made of Mo instead of poly-Si.

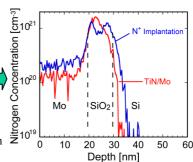

Mo MOS構造に添加した窒素の深さ方向プロファイル。Mo上のTiN層から窒素を拡散させると $SiO_2$ の上方界面にのみ窒素がパイルアップしダメージの無い仕事関数変調が可能。

In-depth profile of N in Mo gate MOSFET. Nitrogen diffusion from TiN on Mo gives rise to nitrogen pileup at the upper interface of SiO<sub>2</sub> that leads to damageless workfunction shift.

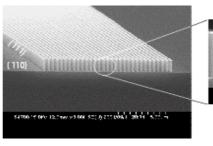

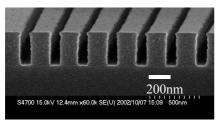

#### 三次元立体MOSFETの研究 (3-D MOSFETs)

ULSIデバイスのさらなる高性能化を目指し、三次元立体MOSトランジスタの研究をおこなっている。 特に単位平面あたりの駆動電流を増大することを目指している。

Research on three-dimensional (3-D) MOS transistor has been carried out aiming for higher performance of ULSI device, larger current-drivability in particular.

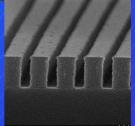

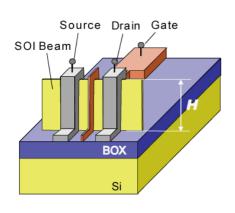

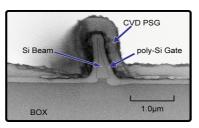

ビーム高さ*Hと*ゲート長*L*のアスペクト比 *H/L*の増大を目的としたSOI (Silicon-On-Insulator) ビームチャネルトランジスタ An SOI (Silicon-On-Insulator) beam-channel transistor aiming for higher aspect-ratio *H/L*, beam height to gate length.

アスペクト比5のビーム チャネルトランジスタ A beam-channel transistor having an *H/L*= 1.0μm / 0.2μm.

幅80nm、高さ1.0 μmのシリコンビームを31本形成して単位平面当たりの駆動電流を数倍高めた櫛形チャネルトランジスタ A corrugated-channel transistor with 31 silicon beams of 80 nm in width and 1.0 μm in height resulting in several-times larger drive current.

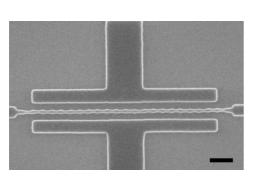

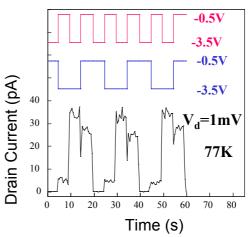

#### シリコン新機能デバイスの研究 (Si New Functional Devices)

次世代シリコン超大規模集積回路 (Ultra Large-Scale Integration, ULSI)のために、 量子効果や単一電子効果を用いて新しい機能を持たせたデバイスや超低消費電力デバイス の研究を行っている。

For next generation ultra large scale integrated circuit (ULSI), researches of new Si functional devices such as Si quantum devices or single electron transistor (SET) are carried out.

200nm

2重サイドゲート及び高ドープ多重ドットを持つSi単一電子トランジスタのSEM像

SEM image of Si SET with double side gates and a highly doped narrow channel with an array of nanoscale islands.

2重サイドゲート型Si単一電子トランジスタ を用いたEXNOR動作

EXNOR characteristics of the Si SET with double side gates.

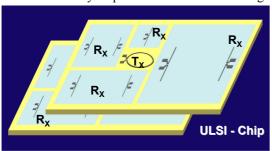

#### ワイヤレスインターコネクトの研究 (Wireless Interconnects)

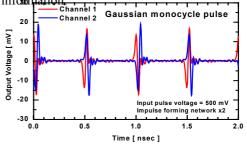

電磁波を用いて超高集積回路の超高速クロックおよびデータ伝送をインパルス無線で実現する ワイヤレスインターコネクトの研究を行っている。シリコンチップ上にアンテナを集積化し、ガウ シアンモノサイクルパルスを用いたウルトラワイドバンド送信回路、受信回路を設計することに よって、超大容量超高速情報伝送を可能にする。

Research on wireless interconnection for high speed clock and data transmission between ULSI chips is conducted. Silicon integrated antenna and ultrawide band (UWB) transmitter and receiver circuits using Gaussian monocycle pulses can transmit ultralarge capacity of information.

$T_X$  : 送信アンテナ、Transmitting antenna  $R_X$  : 受信アンテナ、Receiving antenna

シリコン基板上に集積化したアンテナによる無線の 配線で集積回路間でコミュニケーションが可能

Wireless interconnects integrated on a silicon substrate can transmit signals between ULSI chips.

$$C = B \log_2 \left(1 + \frac{S}{N}\right)$$

C:伝送情報量(Capacity) B:信号の帯域(Bandwidth) S/N:信号雑音比(S/N ratio)

シャノンの理論(上式)により、ガウシアンモノサイクルパルス(右上図)と呼ばれる非常に短い時間のパルス信号の周波数成分はウルトラワイドバンドと呼ばれる超広帯域を持つ(右下図)ため大容量情報伝送が可能である。

According to Schannon's theory, Gaussian monocycle pulse which has an ultrawide band can transmit ultralarge information density.

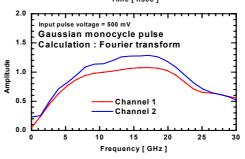

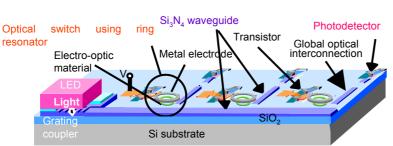

### 光配線LSIの研究 (Optically Interconnected LSI)

光配線は、高速で、分岐数を増しても遅延時間が延びず、並列処理演算に適している。図に示すように電気光学材料を用いた光スイッチの集積化を目指している。

For the optical interconnection the signal delay is not increased with increasing the number of fan out. Therefore, it is suitable for the massively parallel processing. As indicated in the figures, we are focusing on the research to integrate the optical switches using electro-optic materials, for which the refractive index is changed by the applied bias, on the Si chips.

提案している光スイッチを集積した光配線LSI The proposed optically interconnected LSI with optical switches.

電気光学材料とリング光共振器を 用いた光スイッチ

Ring resonator type optical switch using electro-optic material.

作製したリング共振器 Fabricated ring resonator.

電気光学材料( $(Ba, Sr)TiO_3$ )を用いた 光導波路からの出射光

Output light from the waveguide made of electro-optic material ((Ba,Sr)TiO<sub>3</sub>).

# ナノプロセス研究領域

## Nanoprocess Research Division

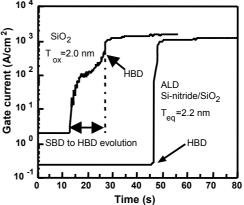

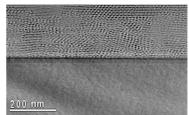

#### 原子層成長ゲート絶縁膜の研究

(Atomic-Layer-Deposition of Ultrathin Gate Dielectrics)

デバイスの超高集積化に伴い、SiO<sub>2</sub>に代わる高誘電率ゲート絶縁膜の開発が不可欠となっている。この候補としてSi窒化膜、ジルコニウム酸化膜やハフニウム酸化膜およびそれらの積層構造の原子層成長法についての研究を行っている。

For high density device integration, development of high-k gate dielectrics are inevitable. Researches of atomic-layer deposition of such gate dielectrics are carried out for high reliability. ZrO<sub>2</sub>, HfO<sub>2</sub>, Si nitride and their stack structures are studied.

Boron

ALDSi<sub>3</sub>N<sub>4</sub>

SiO<sub>2</sub>

drain

原子層成長Si窒化膜/SiO<sub>2</sub>スタックゲート絶縁膜構造 Schematic of ALD Si nitride/SiO<sub>2</sub> stack gate dielectrics.

Si-substrate

原子層成長Si窒化膜/SiO<sub>2</sub>スタックゲート 絶縁膜の絶縁破壊特性

Time dependent dielectric breakdown characteristics of the ALD Si nitride/SiO<sub>2</sub> gate dielectrics.

#### 微細加エプロセスの研究

(Fabrication Processes of Nano-MOSFETs)

微細MOSトランジスタのソース/ドレインと金属配線を接続する微細コンタクトホールの形成および金属埋め込みの研究を行っている。

Small size contact hole formation and metal filling into the holes are studied in order to connect the source/drain of the small MOS transistors with the metal interconnection.

#### 多層配線材料プロセスの研究

(Interconnect and Low-k Materials and Processes)

ULSI配線技術においては、信号の高速伝搬のために低抵抗配線および低誘電率層間絶縁膜材料開発が必須であり、感光性や自己組織化による低誘電率層間絶縁膜をはじめとする新しいコンセプトの次世代配線材料を開発している。

ULSI interconnect technology requires low- resistance metal and low-k dielectrics so that novel low-k dielectric films such as photosensitive and self-assembled low-k films have been developed for the next generation materials.

感光性低誘電率層間絶縁膜の電子線ビームによる直接加工 Electron beam lithography of photosensitive low-k dielectric film.

-自己組織化周期構造ポーラスLow-k絶縁膜の断面 TEM写真

Transmission electron microscopy of periodic porous low-k dielectric film.

# 分子集積機能研究領域

### Molecular Assembly and Materials Synthesis Research Division

### 界面化学結合状態・電子状態の高感度分析と精密制御の研究

#### (Precision Analysis and Control of Chemical and Electronic States at Interfaces)

、 高誘電率ゲート絶縁膜や光電融合デバイスの実現にむけ、半導体界面やヘテロ接合界面における原子スケール構造分析と高感度欠陥密度計測に基づいて、界面制御技術の研究をおこなっている。

For high-k dielectric gate stack and optoelectronic devices, process technologies for precise interface control have been developed based on the analyses of atomic-scale chemical structure and electrically-active defects at the interfaces and hetero-interfaces.

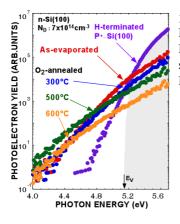

光電子収率分光による高感度欠陥密度計測.  $O_2$ 熱処理が  $HfO_2/SiN_x/Si(100)$ スタック構造の欠陥密度分布に及ぼす影響。 High-sensitive measurements of defect states by total photo-electron yield spectroscopy. Impact of  $O_2$  anneal on the defect state distribution in the  $HfO_2/SiN_x/Si(100)$  stack structure.

$O_2$ 熱処理前後の $HfO_2$ / $SiN_x$ /Si(100) スタック構造のX線光電子分光分析。 界面酸化反応の進行に伴ってN原子が拡散。

X-ray photoelectron spectroscopy of  $HfO_2/SiN_x/Si(100)$  stack structures before and after  $O_2$  anneal. N atoms diffuse with progressive interfacial oxidation.

### 自己組織化プロセスによるSi量子ドット不揮発性メモリの研究

### (Si-Quantum Dot Memory with Self-Assembling Synthesis)

分子あるいは半導体表面の物理化学的性質を利用して、自己組織的に、記憶や論理機能等を持つナノ構造を 形成する研究をおこなっている。

Self-assembling synthesis of functional units such as memory and logic is being studied utilizing self-assembling processes in which the specific or chemical natures of a source gas or substrate surface control the reactions.

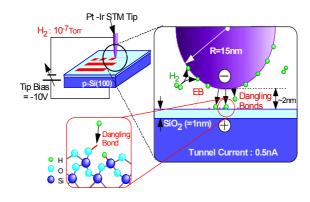

水素雰囲気中でSTMプローブにより位置制御して電気化学的にOH終端を形成した $SiO_2$ 表面 An electro-chemically OH-terminated  $SiO_2$  surface formed by STM probe in  $H_2$  ambient.

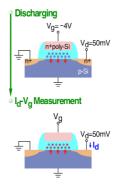

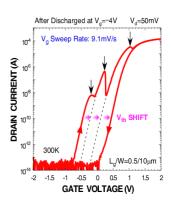

Si量子ドット不揮発性メモリの構造とSi量子ドット 不揮発性メモリの動作

Structure of non-volatile Si-quantum dot memory and its characteristics of the memory operation.

# システム設計・アーキテクチャ研究領域

# System Design and Architecture Research Division

メモリベースと知能情報処理のシステムを実現するために、マルチポートメモリ、連想メモリ及び、メモリベースの学習及び、画像認識と学習のシステムアーキテクチャに焦点を当て研究を行っている。

In order to realize memory-based and intelligent information-processing systems, research focuses on multi-port memories, associative memories, memory-based learning as well as system architectures with visual recognition and learning capability.

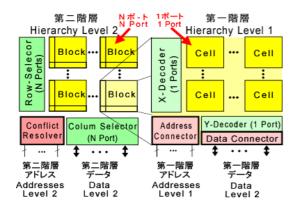

### 多ポートメモリの研究 (Multi-Port Memories)

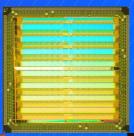

階層型多ポートメモリアーキテクチャ Hierarchical multi-port-memory architecture.

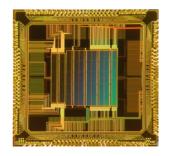

連想メモリの研究 (Associative Memories) 大きなランダムアクセスバンド幅を必要とするシステムの要求を満足するために、 我々は、小面積かつ低アクセス競合確率で実現可能な新しいマルチポートメモリアーキテクチャを開発している。 複数命令同時発行マイクロプロセッサのレジスタファイルやキャッシュへの応用に関する研究も行っている。

To satisfy the system requirement for large random-access bandwidth, we are developing new multi-port-memory architectures, which realize small area consumption as well as low access-conflict probability. Conventional applications such as register-file and cache for advanced multi-issue microprocessors are also studied.

| Technology       | 0.18 µm CMOS       |  |  |

|------------------|--------------------|--|--|

| Routing Levels   | 5 Al Layers        |  |  |

| Supply Voltage   | 1.8 V              |  |  |

| Die Area         | 5.8mm × 5.8mm      |  |  |

| Port Number      | 4 Port             |  |  |

| Storage Capacity | 128 Kbit           |  |  |

| Bank Capacity    | 2 Kbit             |  |  |

| Bank Number      | 16(Tag) + 64(Data) |  |  |

| Word Length      | 16 or 64 bit       |  |  |

| Cycle Time       | 2.5 nsec           |  |  |

4 ポートキャッシュのチップ設計例 Design example of 4-port cache.

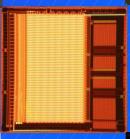

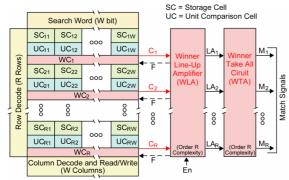

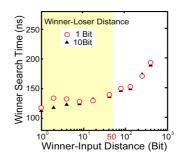

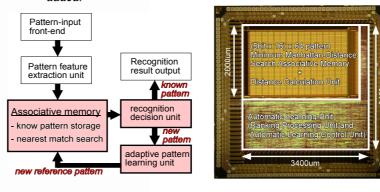

知能システムの認識機能を実現するために重要な基本要素は 連想メモリである。我々は、リアルタイムでの動画認識が可能 な全並列型小面積連想メモリアーキテクチャを開発している。

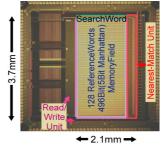

An important basic component for realizing the recognition function of intelligent systems is the associative memory. We develop a fully-parallel compact associative-memory architecture to enable real-time recognition even for objects in motion pictures.

全並列連想メモリアーキテクチャ Fully parallel associative-memory architecture.

マンハッタン距離と 1 2 8 参照データを有するテストチップ設計 Manhattan-distance test-chip design with 128 reference patterns.

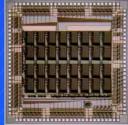

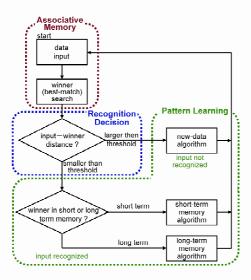

### メモリベース学習の研究 (Memory-Based Learning)

学習アルゴリズムの例 Example for learning algorithm.

知能情報処理システムには学習機能が不可欠である。 我々は連想メモリに学習機能を追加する可能性について 研究を行っている。これを実現するために、例えば人間 の学習機構を模倣した、長期記憶と短期記憶の原理を導 入している。

Intelligent information processing systems require a learning function. We study the possibilities of realizing learning as an addition of the associative memory. For this purpose an organizational principle, as e. g. short- and long-term storage is added.

64参照パターン(長期記憶40,短期記憶24)の上記の学習アルゴリズムを実現した連想メモリテストチップ

Test chip with 64-pattern (40 long term, 24 short term memory) associative memory realizing above learning algorithm.

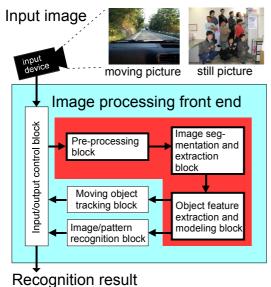

### 画像分割と特徴抽出の研究 (Picture Segmentation and Feature Extraction)

画像認識システムの概要 System overview for picture recognition.

知能情報処理のためのプロトタイプシステムとして、リアルタイム画像認識について研究を行っている。このようなシステムには、連想メモリの機能とメモリベースの学習機能に加えて、画像分割と特徴抽出の機能が必要である。そこで、我々は集積化が容易に行うことが可能な画像分割と特徴抽出の新しい手法を現在研究している。

Real-time picture recognition is investigated as a prototype system for intelligent information processing. In addition to the associative memory function and memory based-learning, the functionality of picture segmentation as well as feature extraction is necessary for such systems. Therefore we are developing new methods for picture segmentation and feature extraction, which allow easy integration.

Input Image Size: 640 x 480 (VGA image) (in case of SIA) High-Speed Processing: 7.49 msec@10MHz (simulation) Low Power Dissipation: 30 mW@10MHz (simulation)

画像分割テストチップ Picture segmentation test chip.

## 大学院先端物質科学研究科半導体集積科学専攻における教育 Education at Department of Semiconductor Electronics and Integration Science, Graduate School of Advanced Sciences of Matter

ナノデバイス・システム研究センター教員は大学院先端物質科学研究科半導体集積科学専攻に所属している。下記のナノデバイス工学、ナノプロセス工学、ナノ集積工学、知能集積回路工学の4つ研究分野において研究だけでなく、大学院博士課程教育も行っている。

Faculty members at the Research Center for Nanodevices and Systems belong to the Department of Semiconductor Electronics and Integration Science, Graduate School of Advanced Sciences of Matter, Hiroshima University. Nanodevice Engineering, Nanoprocess Engineering, Nanoscale Integration Engineering and Intelligent Integrated Circuits Engineering Laboratories conduct not only research but also graduate level education for M.S. and Ph.D. degrees.

#### 大学院先端物質科学研究科 半導体集積科学専攻の研究室

Laboratories of Department of Semiconductor Electronics and Integration Science

| Education of Bolantinian of Commoditation Electronia and Integration Colonics |                                                                                                                                         |                                                                 |  |  |  |  |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| 研究室<br>Laboratory                                                             | 教育研究内容<br>Content of education and research                                                                                             | 担当教官<br>Staff                                                   |  |  |  |  |

| 量子半導体工学<br>Semiconductor Devices and<br>Materials                             | 量子構造新機能デバイス<br>Silicon-based novel functional devices<br>with quantum structures<br>超微細デバイス・プロセス<br>Materials and processes integration | 宮崎 誠一<br>Seiichi Miyazaki<br>東 清一郎<br>Seiichiro Higashi         |  |  |  |  |

| 極微細デバイス工学<br>Ultra-small Devices<br>Engineering                               | 極微細デバイスモデリング<br>MOSFET modeling<br>光応答デバイス<br>Optical and electromagnetic response<br>devices                                           | 三浦 道子<br>Mitiko Miura<br>樋口 克彦<br>Katsuhiko Higuchi             |  |  |  |  |

| 機能集積システム工学<br>Integrated Systems                                              | アナログ・アナデジ混載回路設計<br>Circuits and design for analog and AD<br>mixed LSIs                                                                  | 岩田 穆<br>Atsushi Iwata<br>佐々木 守<br>Mamoru Sasaki                 |  |  |  |  |

| ナノデバイス工学<br>Nanodevice Engineering                                            | 極限微細デバイス<br>Ultra-small nanodevices<br>ワイヤレス信号伝送・高速配線<br>Wireless signal transmission and high-<br>speed interconnection                | 吉川 公麿<br>Takamaro Kikkawa<br>芝原 健太郎<br>Kentaro Shibahara        |  |  |  |  |

| ナノプロセス工学<br>Nanoprocess Engineering                                           | 原子スケール加工技術・ナノプロセス<br>Atomic scale fabrication and nano process                                                                          | 横山 新<br>Shin Yokoyama<br>中島 安理<br>Anri Nakajima                 |  |  |  |  |

| ナノ集積工学<br>Nanoscale Integration<br>Engineering                                | 極限立体集積回路実現のデバイス<br>3D-integrated circuit devices                                                                                        | 角南 英夫<br>Hideo Sunami                                           |  |  |  |  |

| 知能集積回路工学<br>Intelligent Integrated Circuits<br>Engineering                    | メモリベースの知能情報処理,<br>LSI回路設計<br>Memory-based intelligent<br>information processing and LSI<br>circuits design                              | マタウシュ H. J.<br>Hans Jürgen Mattausch<br>小出 哲士<br>Tetsushi Koide |  |  |  |  |

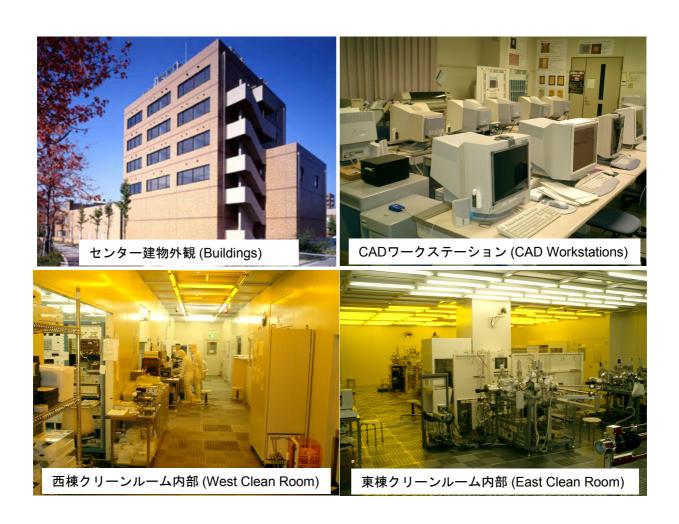

# ナノデバイス・システム研究センターの設備 Facility of Research Center for Nanodevices and Systems

建物面積 (Area of the Buildings)

単位 (unit) m<sup>2</sup>

| 設立(Building<br>Construction)                          | クリーンルーム<br>Clean Room | 管理研究棟<br>(Office & Res. Area) | 合計 (Total)      |             |                                |  |  |

|-------------------------------------------------------|-----------------------|-------------------------------|-----------------|-------------|--------------------------------|--|--|

| 旧集積化システム研究<br>センター既設部(West<br>Building) (1988. 12)    | 520                   | 790                           | 1310            | = min       |                                |  |  |

| ナノデバイス・システム<br>研究センター新設部<br>(East Building)(1998. 10) | 310                   | 1460                          | 1770            | 5階<br>4階 La | aboratories                    |  |  |

| 合計 (Total)                                            | 830                   | 2250                          | 3080            | 3階          | 実験室・研究室                        |  |  |

| クリーンルームクラス (Clean Room Class)10, 0.1 μm 実験室・研究室       |                       |                               |                 |             |                                |  |  |

| 2階                                                    |                       |                               |                 | ZPA .       | 実験室・研究室                        |  |  |

| 1階                                                    |                       | 开究室<br>文學<br>新理室<br>West      | ンルー.<br>Clean R |             | フリーンルーム (2)<br>east Clean Room |  |  |

|                                                       |                       | 西棟 (West Building) 東棟         |                 |             | (East Building)                |  |  |

# 主な装置 Principal Equipment

熱酸化及び減圧CVD装置 Oxidation furnaces and lowpressure CVD reactors.

高速熱処理装置 Rapid thermal annealing system for dopant activation (Samco HT-1000) 200℃/sec.

イオン注入装置 Ion implanter for doping (As, Sb, B, In, Si, Ar, He). 200 keV, 100 µA (ULVAC IM200).

多結晶シリコン用ICPエッチャー ICP etcher for poly-Si.

極微細パターン形成のためのドライエッチング装置 Dry etchers for ultra fine patterning.

i線ステッパー i-line optical stepper (Nikon i8a).

電子線描画装置 EB lithography system (Hitachi HL-700DII). 最小 線幅 (Feature Size) 50nm.

配線金属堆積用スパッタ装置 Sputtering system for metallization (Al, Ti, TiN).

二次イオン質量分析器 Secondary Ion Mass Spectrometry (SIMS) (Phi 6500). O and Cs beams.

電界放出型透過電子顕微鏡 Transmission Electron Microscopy (TEM, Hitachi HF-2100) 200kV.

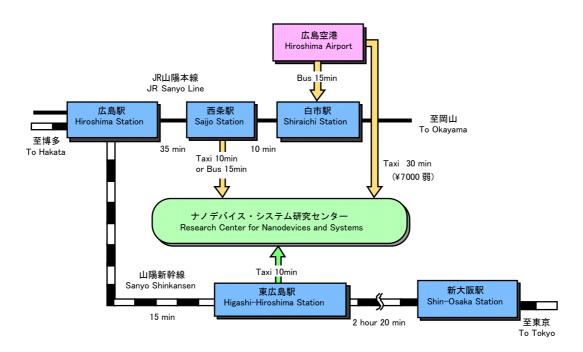

- ・JR山陽本線広島駅から西条駅まで35分

- ・西条駅または山陽新幹線東広島駅から、バス(広 大東ロ下車)またはタクシーで10~15分

- ・広島空港よりタクシーで約30分(¥7000弱)、またはバスでJR白市駅経由約1時間

- ・新大阪駅から山陽新幹線で東広島駅経由約3時間

- 35 minutes from Hiroshima station to Saijo Station by JR Sanyo Line

- 10 to 15 minutes by bus or taxi from Saijo Station or Sanyo Shinkansen, Higashi-Hiroshima Station

- About 30 minutes by taxi (about ¥7000), or about 1 hour by bus and train via JR Shiraichi Station from Hiroshima Airport

- About 3 hours via Sanyo Shinkansen Higashi-Hiroshima Station from Shin-Osaka Station

広島大学ナノデバイス・システム研究センター

〒739-8527 東広島市鏡山1-4-2

TEL: (082) 424-6265 FAX: (082) 422-7185

E-mail: rcns@hiroshima-u.ac.jp

Research Center for Nanodevices and Systems, Hiroshima University

1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan

Phone: +81 (82) 424-6265

Fax: +81 (82) 422-7185

E-mail: rcns@hiroshima-u.ac.jp

ホームページ、Home page: http://www.rcns.hiroshima-u.ac.jp/